高速互连链路常见的阻抗不连续点:

1.芯片封装:通常芯片封装基板内的PCB走线线宽会比普通PCB板细很多,阻抗控制不容易;

2.PCB过孔:PCB过孔通常为容性效应,特征阻抗偏低,PCB设计最应该关注与优化;

3.连接器:连接器内铜互连链路的设计要同时受到机械可靠性与电气性能的双重影响,在两者之间寻求平衡;

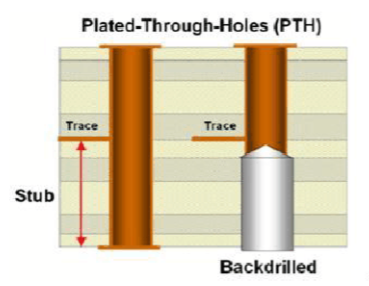

PCB的过孔通常为通孔设计(从Top表层贯通到Bottom底层),当连接过孔的PCB走线比较靠近TOP层时,就会在PCB互连链路的过孔处产生“Stub”分叉,造成信号的反射、影响信号质量,这种影响对于越高速的信号影响越大。

高速互连链路的S参数曲线,绿色标识No Backdrill的曲线为互连链路的插损,可以看到在4.0~4.5GHz频点存在明显的最大谐振,这种谐振从2.5GHz频点已经开始显现。PCB通孔的Stub影响,一方面体现在阻抗连续性的破坏,另一方面体现在链路高频损耗的恶化。因此,需要想办法把PCB通孔的Stub去除,“背钻”(Backdrill)就是这样一种PCB加工技术。

Backdrill的加工方法简介

背钻技术就是利用控深钻孔方法,采用二次钻孔方式钻掉连接器过孔或者信号过孔的Stub 孔壁。通孔成型后,通过从“背面”的二次钻孔,去除PCB通孔的多余Stub,当然Backdrill钻头的直径要大于通孔的孔直径,而且要根据加工钻孔的深度工艺公差水平在“不能破坏PCB孔与走线连接”的基础上保证“剩余Stub长度尽可能小”,即所谓的“控深钻孔”。

上图为通孔BackDrill剖面示意图:左边为正常的信号通孔;右边为Backdrill后的通孔示意图,表示从Bottom层一直钻到走线Trace所在的信号层。

三、BackDrill在PCB设计中的规则

1.压接连接器PCB孔的“剩余孔壁长度”,要求:L≥L1+12mil

2.背钻孔深度控制建议在两层之间,两层之间厚度要求≥12mil。举例说明:背钻孔1,当相邻两层(如L12/L13、L13/L14)间距不满足≥12mil,而L12/L14层间距≥12mil时,推荐背钻孔深控制在L12/L14之间;背钻孔2/3,当L9/L10层间距≥12mil 时,推荐背钻孔深控制在L9/L10之间。

3.PCB走线到背钻孔的间距,PCB走线到背钻孔边缘距离≥10mil。

4.背钻孔的孔径尺寸,背钻孔径(D)=钻孔直径(d)+10mil

通常的认识:≥5Gbps速率的信号需要考虑增加Backdrill设计。

当然,高速板高速互连链路的设计是个系统工程,如果芯片驱动能力足够强,亦或系统互连链路不那么长,也许不做Backdrill设计信号质量同样能过关。所以最靠谱的做法还是通过系统互连链路仿真的方法来确定是否需要Backdrill。

ATCA架构系统的高速互连链路,高速Serdes信号速率3.125Gbps,链路互连总长度40inch,不幸的是芯片驱动能力偏弱,信号会偶发误码,尝试多种整改手段无效。最后尝试了对Backplane背板的连接器通过做Backdrill处理,误码小时、问题解决。也许此案例中的芯片驱动能力就差Backdrill对链路性能改善那么一点点效果吧。