数据中心与5G通信的引擎舱里,光模块正以惊人的速度迭代。每一次传输速率的跃升,从400G到800G,再到令人屏息的1.6T,都不仅仅是数字的狂欢,更是对物理层基础技术的一次极限施压。这场静默革命的核心战场之一,就悄然隐藏在那片承载着所有精密电路的PCB(印制电路板)之中。而“阻抗控制”,正是这个微观战场上决定信号“生死”的终极指挥官。它绝非生产线上的一个普通参数,而是一套贯穿概念、设计、物料与制造的精密封装艺术,是高速信号能否完整、准确抵达彼岸的基石。

在手指甲盖大小的光模块内部,密布着上百条细如发丝的传输线。它们不是简单的铜线,而是承载着每秒数百亿比特数据的“信息高速公路”。阻抗,就是这条高速公路的“特征通行标准”——它必须全程均匀一致。任何一处意外的“收费站”或“路面缩窄”(即阻抗失配),都会导致高速行驶的“信号车队”发生混乱、碰撞和能量泄露,最终表现为数据误码、性能急剧下降。因此,将PCB的阻抗变化控制在理论设计值±5%甚至更严格的公差带内,是工程师们必须打赢的一场没有硝烟的战争。

一、 设计先行:在蓝图中植入阻抗的“基因”

一切卓越的工程实现,都始于一张精妙绝伦的蓝图。对于光模块PCB而言,阻抗控制的基因,必须在设计阶段就被精准地编码进去。

叠层架构:构筑稳定的信号地基

多层PCB(例如常见的10层或14层HDI结构)的叠层设计,是阻抗控制的物理基础。这就像为摩天大楼规划承重墙和楼层高度。每一层介质的厚度、所用半固化片(PP)的类型、铜箔的粗糙度与厚度,都共同决定了电场分布,从而影响走线的特征阻抗。设计师必须像一位精算师,依据选定的低损耗材料(如松下M系列、台耀TUC的某些高端型号)的已知介电常数(Dk),通过专业软件进行精密计算,确定出为了实现目标阻抗(如差分100Ω),走线需要多宽、与参考平面距离多少。

走线艺术:描绘流畅的信号路径

有了稳固的地基,还需规划畅通的道路。在高速设计中,走线不再是简单的连接,而是需要精心描绘的传输线。差分对的严格等长、线距的恒定维持是基本操守,用以保证信号同步和抵消共模噪声。而更进阶的艺术在于处理“变道”和“立交”。例如,采用平滑的弧形拐角或“锥形渐变”过渡来替代生硬的直角转弯,可以显著减少因线宽突变引起的阻抗不连续和信号反射。对于芯片引脚扇出区、过孔转换区这些“交通枢纽”,则需要借助三维全波电磁仿真工具进行“压力测试”,预先优化其结构,避免成为信号瓶颈。

二、 材料科学:为高速信号铺设“超导轨道”

精妙的设计,需要极致的材料来实现。如果说设计是梦想,那么材料就是让梦想照进现实的土壤。高速光模块PCB对材料的苛刻要求,达到了电子工业的顶峰。

基板材料:选择低损耗的“路基本体”

普通消费电子使用的FR-4材料,在数GHz的高频下损耗巨大,已完全无法满足要求。当前主流的高速光模块PCB,普遍采用低损耗(Low Loss)或极低损耗(Very Low Loss)的专用覆铜板。这些特种材料不仅具有更低且更稳定的Dk值,其更关键的指标——损耗因子(Df) 值往往比FR-4低一个数量级。这意味着信号在传输过程中的能量衰减被大幅抑制。同时,这些高端材料在玻璃布编织均匀性、树脂固化一致性方面也表现卓越,确保了介质层厚度在整板范围内的微小波动,这是控制阻抗均匀性的物理前提。

导体材料:打磨光滑的“行车路面”

另一个常被忽视的细节是铜箔的表面粗糙度。在低频时,电流贯穿整个导体截面;而在高频下(如10GHz以上),电流会“挤”在导体表面很薄的一层内流动,即“趋肤效应”。此时,粗糙的铜箔表面就像布满碎石的路面,会极大地增加信号“行驶”的阻力,导致额外损耗。因此,采用表面异常光滑的反转铜箔(RTF)或超低轮廓铜箔(VLP),已成为高速PCB的标配。这种对“路面平整度”的极致追求,是降低插入损耗、保持阻抗纯净度的关键一环。

三、 工艺淬炼:在微米世界中实现精准拿捏

设计是理想,材料是基础,而将二者完美结合,则依赖于登峰造极的制造工艺。这是阻抗控制从图纸走向产品的“惊险一跃”,任何微小的偏差都可能导致前功尽弃。

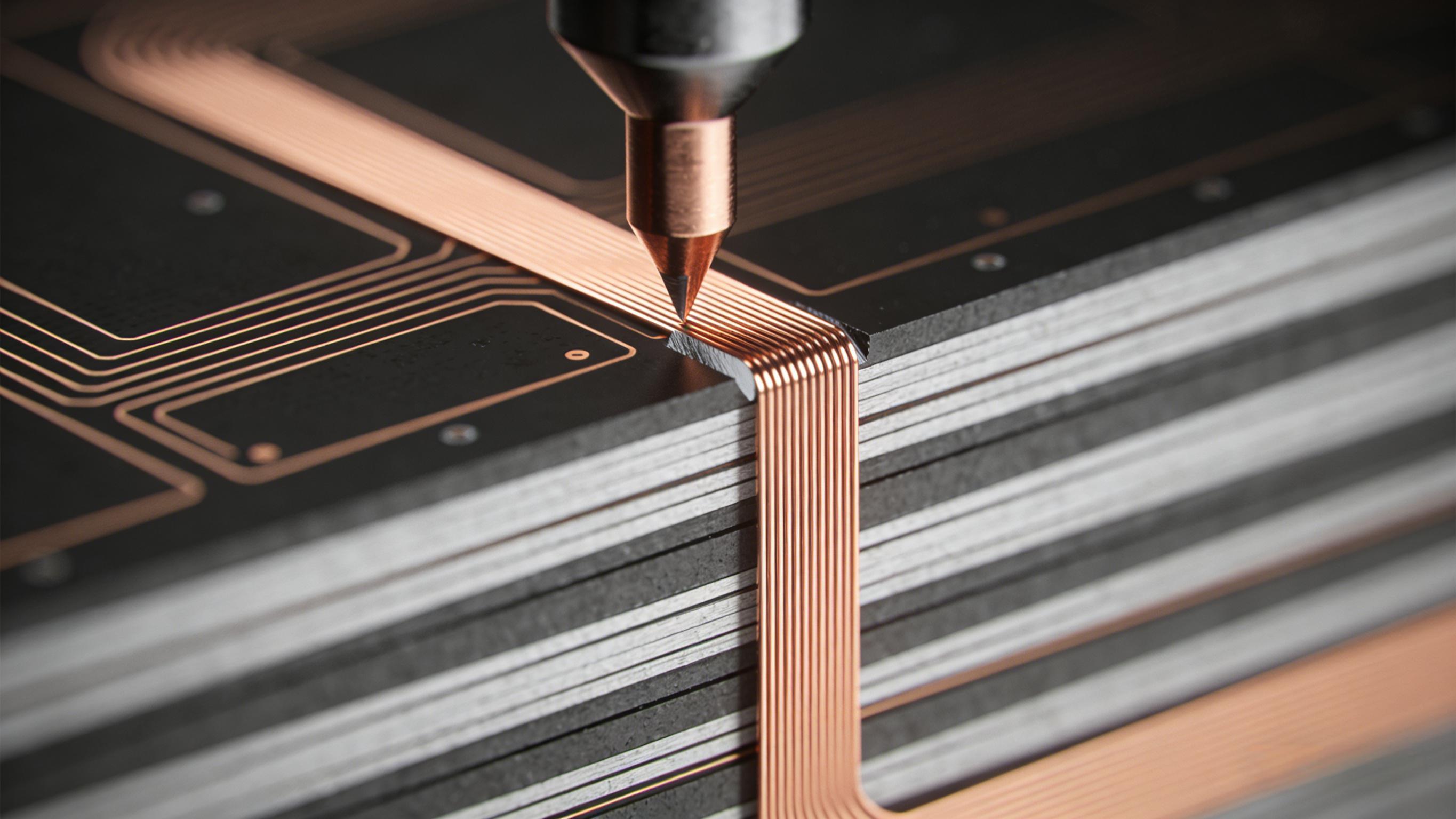

图形转移:刻蚀出分毫不差的线宽

通过曝光和蚀刻将设计图形转移到铜箔上,这一步直接决定了走线的最终宽度。蚀刻是一个化学反应过程,存在“侧蚀”现象,即铜被纵向蚀刻的同时也会横向溶蚀,导致实际线宽略小于设计线宽。工程师必须根据线距、铜厚、药水参数等,精确计算并预设“蚀刻补偿量”,就像射击时需要提前计算风速和弹道下坠一样。对蚀刻速率、药水浓度的实时监控与动态调整,是保证大批量生产中线宽一致性的生命线。

多层压合:掌控以微米为单位的厚度

多层PCB通过将芯板与半固化片叠层加热加压而成。半固化片在压合过程中会流动、填充并固化。这个过程的压力、温度曲线和真空度,直接决定了每一层介质最终的厚度。而介质厚度,是阻抗计算公式中的核心变量之一。压合工艺的窗口必须非常狭窄且稳定,确保每一张生产板、板上的每一处区域,厚度波动都被限制在微米级别。这要求对物料特性、设备状态和环境有超凡的控制力。

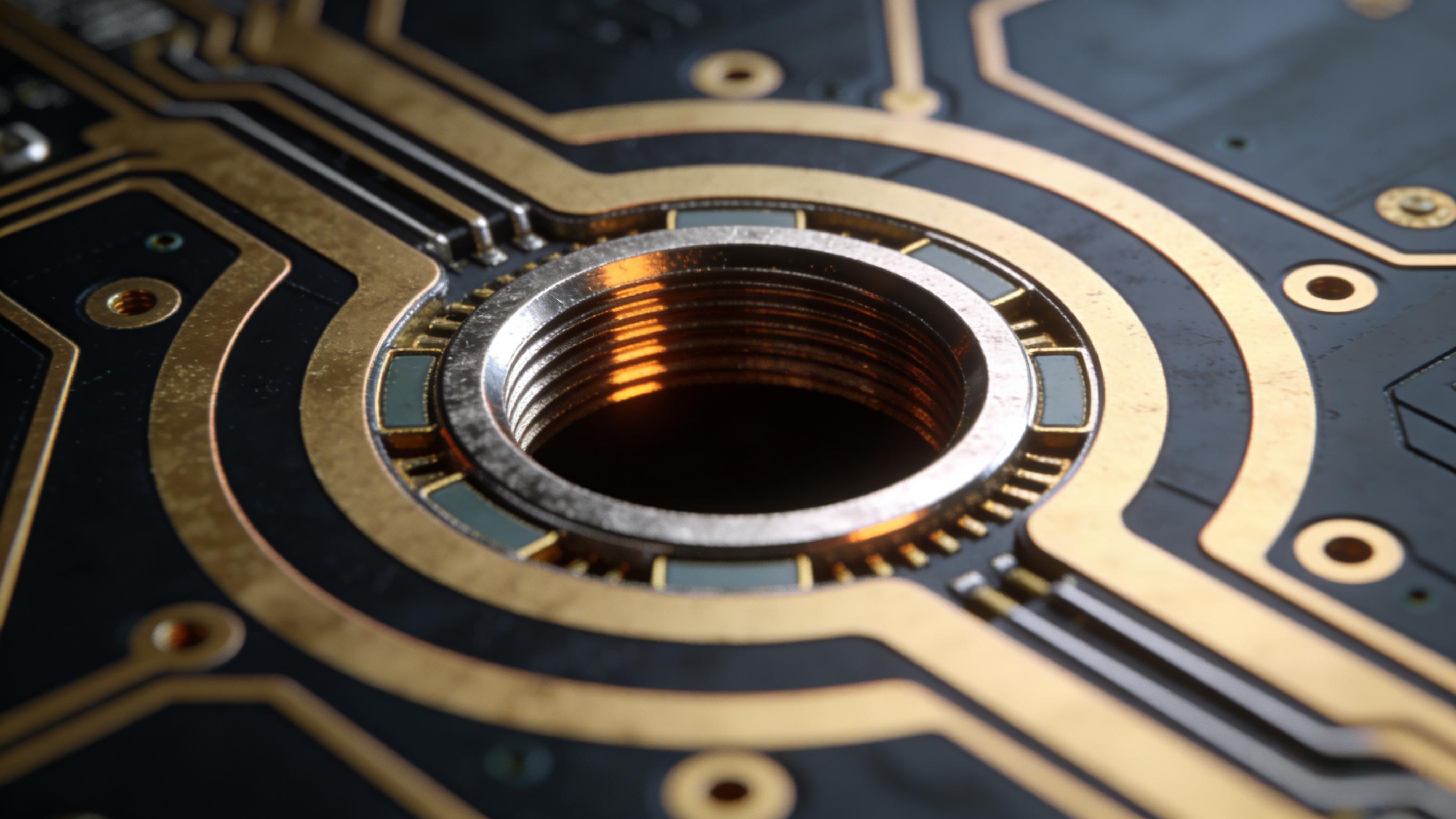

过孔优化:疏通三维互联的“栓塞点”

垂直连通各层的过孔,是破坏二维传输线理想环境的最大挑战。一个简单的通孔会形成巨大的阻抗突降和信号反射。为此,两大关键工艺被广泛采用:一是背钻(Back Drill) ,在通孔电镀后,用钻头将没有电气连接需求的多余孔壁(残桩)钻掉,这根长长的“天线”是导致谐振和反射的元凶;二是精心设计过孔反焊盘(Anti-pad) 的尺寸和形状,在电源/地平面上为过孔让出足够大的空间,优化其电容电感特性,从而改善阻抗连续性。这些工艺增加了成本和复杂度,但对于高速信号而言,是不可或缺的“疏通手术”。

四、 测试验证:用数据为性能签署“通行证”

无论设计与工艺如何自信,最终的裁决权必须交给客观、精确的测量。测试验证是阻抗控制闭环的终点,也是产品性能的最终背书。

仿真预测:在虚拟世界中排除万难

在投入第一块实体板之前,仿真分析是成本最低的“试错”手段。使用Polar Si9000或类似工具进行二维阻抗建模是基础。对于复杂的连接器区域、过孔阵列及不规则的走线拓扑,则必须启动ANSYS HFSS或CST Studio Suite等三维全波电磁仿真器。它们可以近乎真实地模拟电磁场的分布与变化,提前预测出信号完整性指标(如S参数、眼图),并发现潜在的阻抗突变点。仿真与设计的迭代优化,能将大部分风险消灭在萌芽状态。

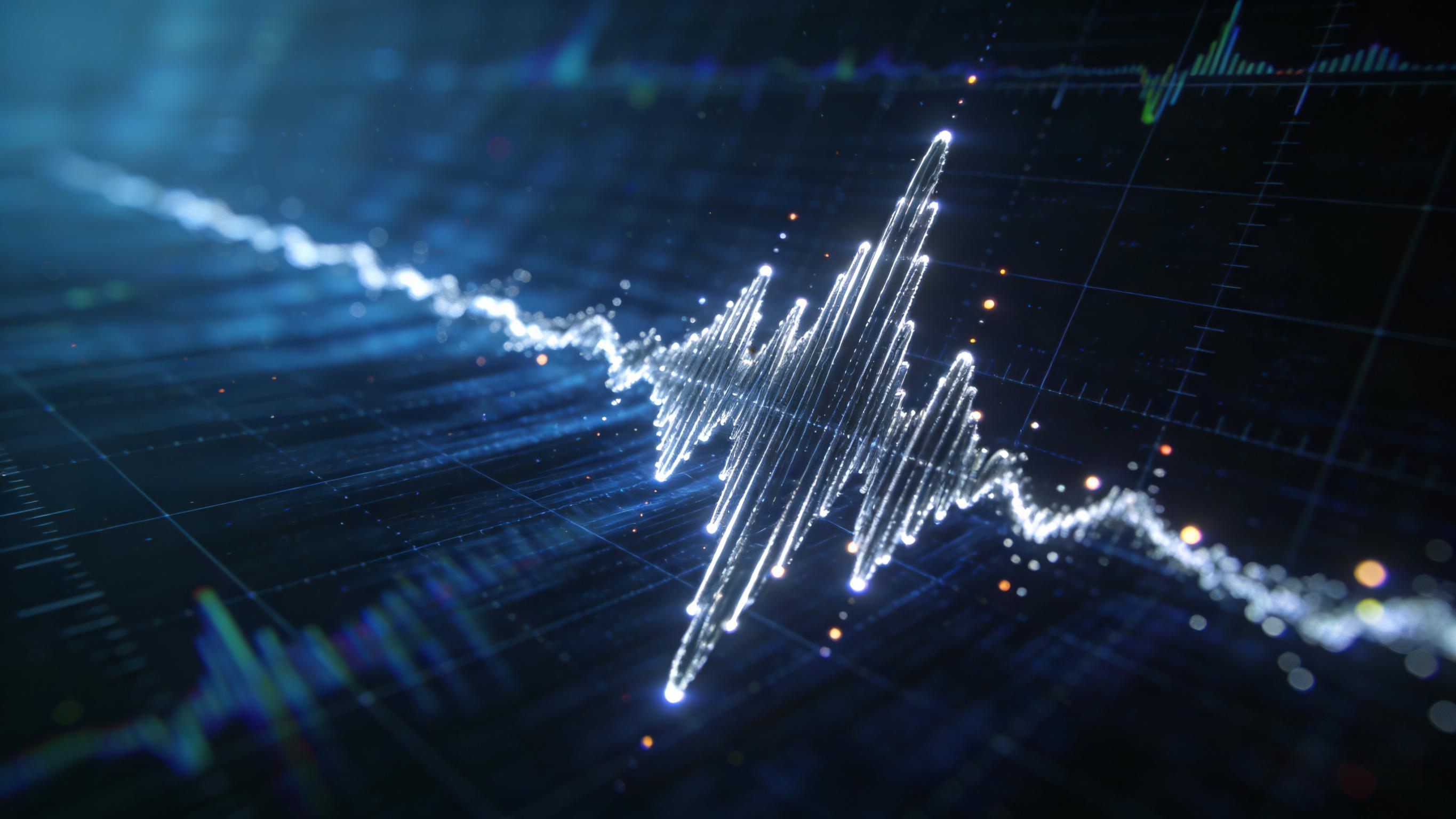

实板测量:用TDR描绘真实的阻抗地图

当第一块工程样品板出炉,时域反射计(TDR) 便成为最权威的“诊断仪”。TDR向待测走线发送一个快速上升沿的阶跃信号,并像雷达一样,通过分析反射信号的时间和幅度,精确计算出信号路径上每一点的阻抗值。最终,仪器屏幕上会呈现一条蜿蜒的曲线,它就像这条信号走线的“心电图”或“海拔剖面图”,清晰地展示出何处平坦、何处有凸起或凹陷。这条曲线必须完全落在设计预设的阻抗公差带内。对于关键的超高速通道,仅TDR还不够,还需进一步在矢量网络分析仪(VNA)上测试其全套散射参数(S参数) ,特别是插入损耗和回波损耗,以全面评估其在频域上的性能。

五、 面向未来:持续演进的控制哲学

光模块PCB的阻抗控制,是一个没有止境的追求。它从单一的电路板设计问题,演变为一个融合了电磁理论、材料化学、精密加工和测试计量学的系统工程。随着CPO(共封装光学)技术的兴起,芯片与光引擎的距离被无限拉近,对封装基板乃至硅中介层中的“超短距”互连提出了亚微米尺度的阻抗控制要求。这将是下一个技术前沿。

回望来路,从10G到1.6T的每一座速率丰碑,都矗立在对应时代阻抗控制精度的台阶之上。它要求设计者有深邃的理论洞察,制造者有工匠般的工艺坚守,更要求从设计到生产、测试的全链条形成共同的语言和标准。掌握这套从蓝图到验证的完整方法论,不仅是打造当下高端光模块产品的核心竞争力,更是叩响未来更高速通信时代大门的必备钥匙。在这条追求信号绝对完整的道路上,每一次对阻抗更精准的掌控,都是对我们所处数字世界基石的一次加固。