随着摩尔定律逐渐逼近物理极限,传统的二维平面封装技术面临诸多瓶颈,如布线密度不足、信号延迟增加以及功耗上升等问题。为此,三维堆叠封装设计应运而生,作为一种先进的集成电路封装方案,它通过将多个芯片或器件在垂直方向上进行堆叠和互连,实现了更高的集成度、更短的互连路径以及更优的性能表现。三维堆叠封装设计不仅代表了半导体封装技术的一次革命性突破,还在人工智能、高性能计算、移动设备等领域展现出巨大潜力。本文将从技术原理、实现方式、优势与挑战、应用案例以及未来趋势等方面,全面解析三维堆叠封装设计,帮助读者深入理解这一关键技术如何推动电子行业的创新。

三维堆叠封装设计的核心在于通过垂直堆叠多个芯片层,利用硅通孔(TSV)等技术实现层间互连,从而在有限的空间内实现更高的功能密度。与传统的二维封装相比,这种设计能够显著缩短信号传输距离,降低功耗,并提升整体系统的可靠性。例如,在智能手机和服务器中,三维堆叠封装可以集成处理器、内存和传感器等多种组件,实现更高效的数据处理。然而,这一技术也面临着热管理、制造成本和工艺复杂性等挑战。本文将系统性地探讨这些方面,为读者提供一个全面的技术视角。

一、三维堆叠封装设计的基本概念与背景

三维堆叠封装设计是一种将多个半导体芯片或器件在三维空间内垂直堆叠并互连的先进封装技术。它起源于20世纪末,随着集成电路尺寸的不断缩小,传统封装方式在性能提升上遇到瓶颈。二维封装通常依赖于平面布线,导致互连长度增加,信号延迟和功耗上升。而三维堆叠封装通过垂直集成,将不同功能的芯片(如逻辑芯片、存储芯片和传感器)堆叠在一起,形成紧凑的模块,从而克服了这些限制。

这种设计的背景与半导体行业的发展紧密相关。早期,封装技术主要关注保护和连接芯片,但随着电子设备向小型化、高性能化发展,封装的作用逐渐扩展到提升系统整体性能。三维堆叠封装的兴起得益于多种技术的进步,例如微细加工技术、材料科学和热管理方案。其中,硅通孔(TSV)技术是关键推动力,它通过在硅基板上制作垂直通道,实现芯片层间的电气连接。TSV技术不仅减少了互连长度,还提高了信号传输速度,使得三维堆叠封装在高性能计算和移动设备中广泛应用。

从行业角度来看,三维堆叠封装设计已成为先进封装市场的重要组成部分。根据市场研究数据,全球三维堆叠封装市场预计在未来几年内保持高速增长,主要驱动力来自5G通信、人工智能和物联网等新兴领域。这种设计不仅提升了芯片性能,还降低了系统成本,因为它允许使用不同工艺节点的芯片进行集成,从而优化资源利用。例如,在内存堆叠中,三维封装可以将DRAM和NAND闪存堆叠在一起,实现更高的带宽和能效。总之,三维堆叠封装设计代表了封装技术从简单保护向系统集成转型的重要里程碑,为未来电子设备的发展奠定了基础。

二、三维堆叠封装设计的技术原理与实现方式

三维堆叠封装设计的技术原理基于垂直集成和层间互连,其核心是通过将多个芯片或器件堆叠在一起,并利用先进互连技术实现高效的数据交换。这种设计的关键在于减少互连距离,从而降低信号延迟、功耗和噪声。实现三维堆叠封装的主要方式包括芯片堆叠、硅中介层和硅通孔(TSV)技术。

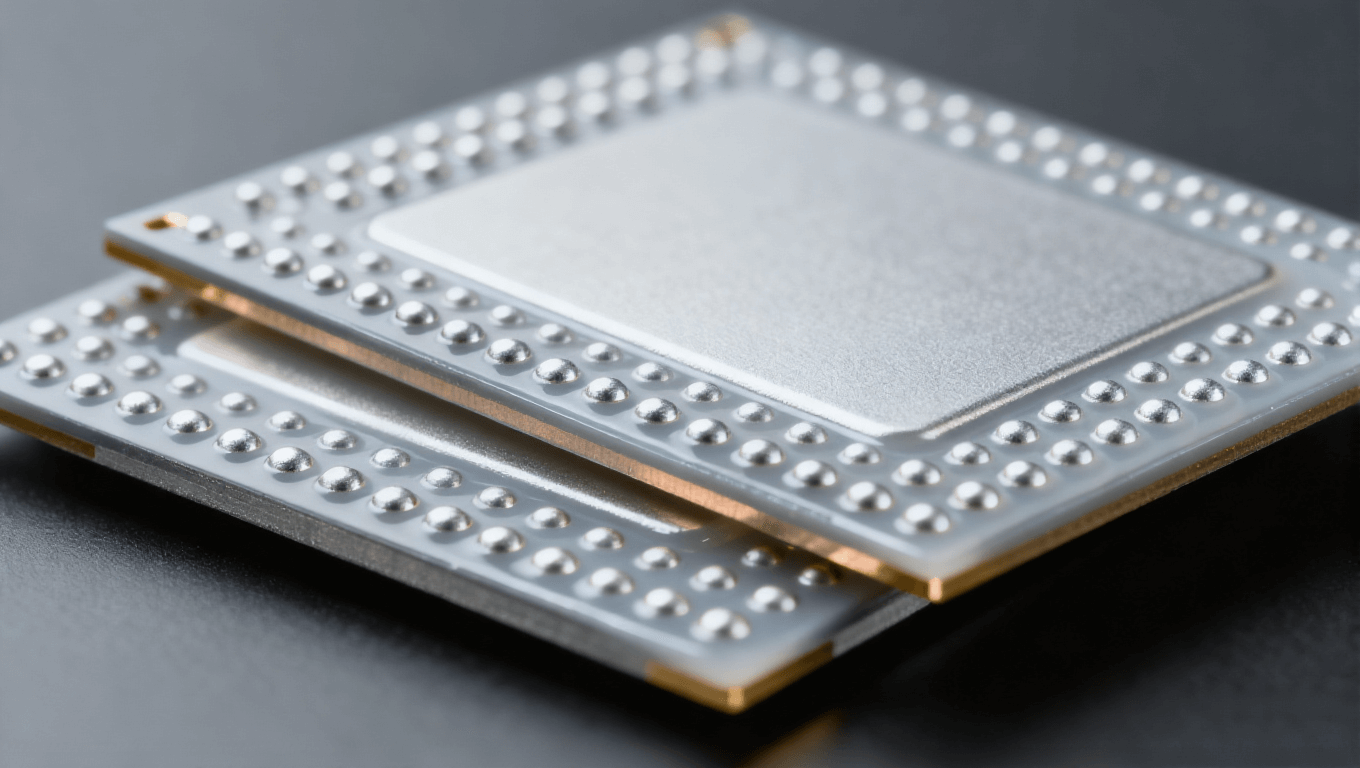

首先,芯片堆叠是三维封装的基础形式,它涉及将多个芯片垂直堆叠并通过焊接或粘合材料固定。堆叠方式可以分为同质堆叠和异质堆叠:同质堆叠指堆叠相同类型的芯片,如多个内存芯片;异质堆叠则集成不同功能的芯片,例如将处理器、内存和传感器组合在一起。异质堆叠更复杂,但能实现更高的系统集成度。在堆叠过程中,芯片之间的间隙通常填充有导热材料,以帮助散热,同时使用微凸块或铜柱进行电气连接。

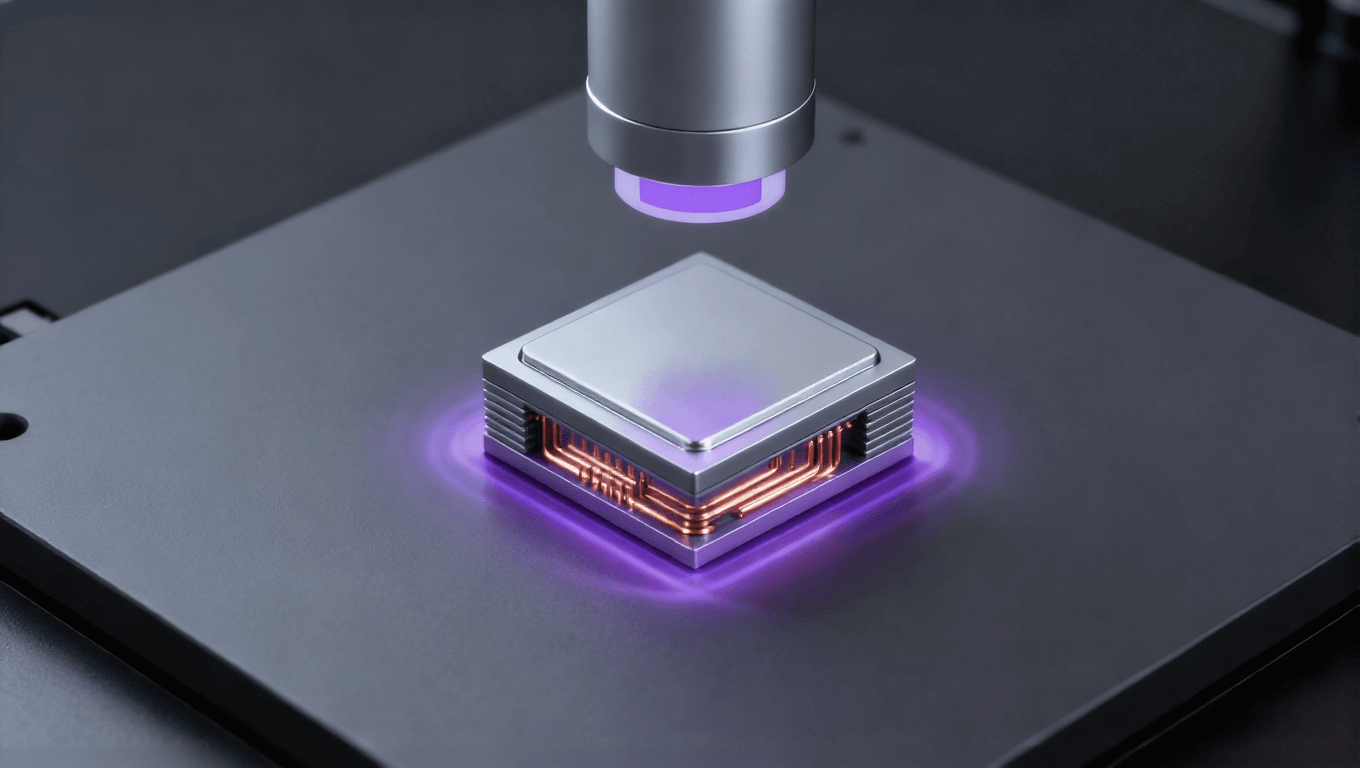

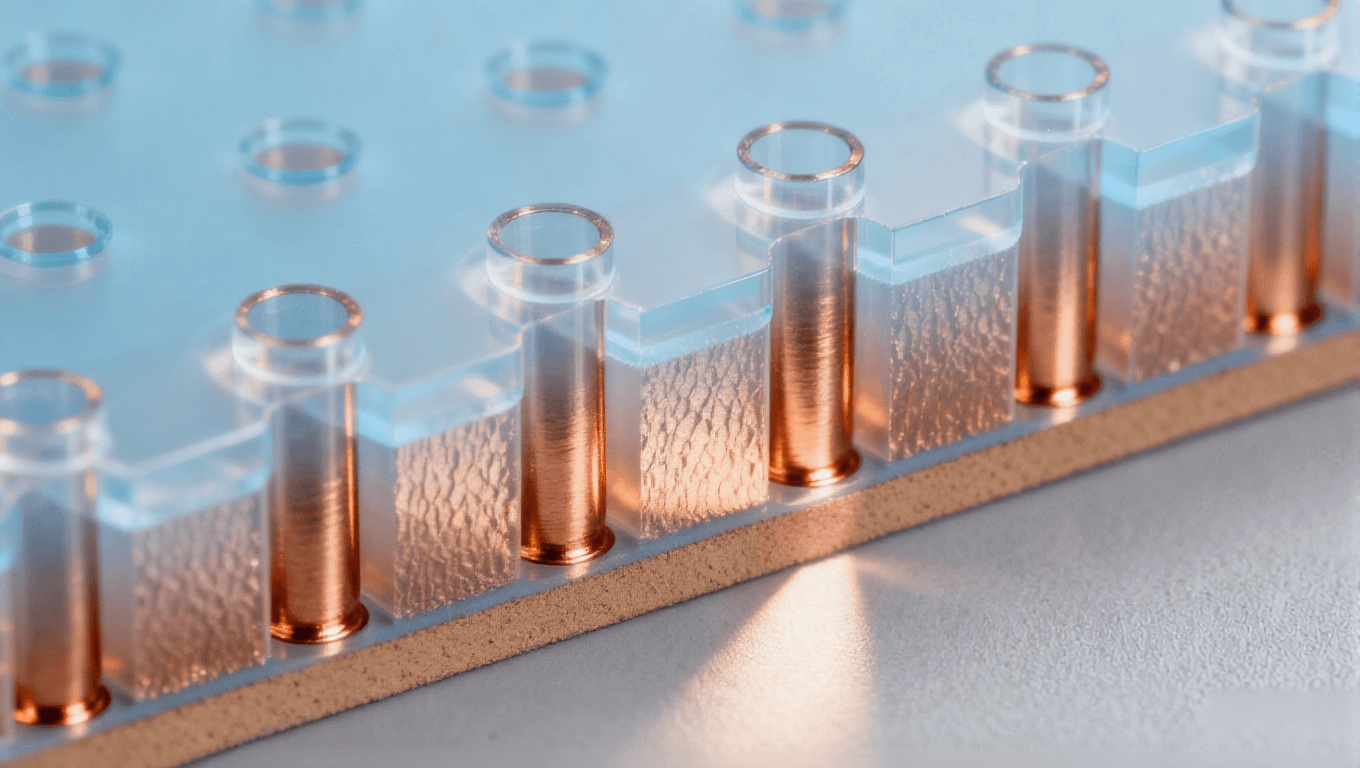

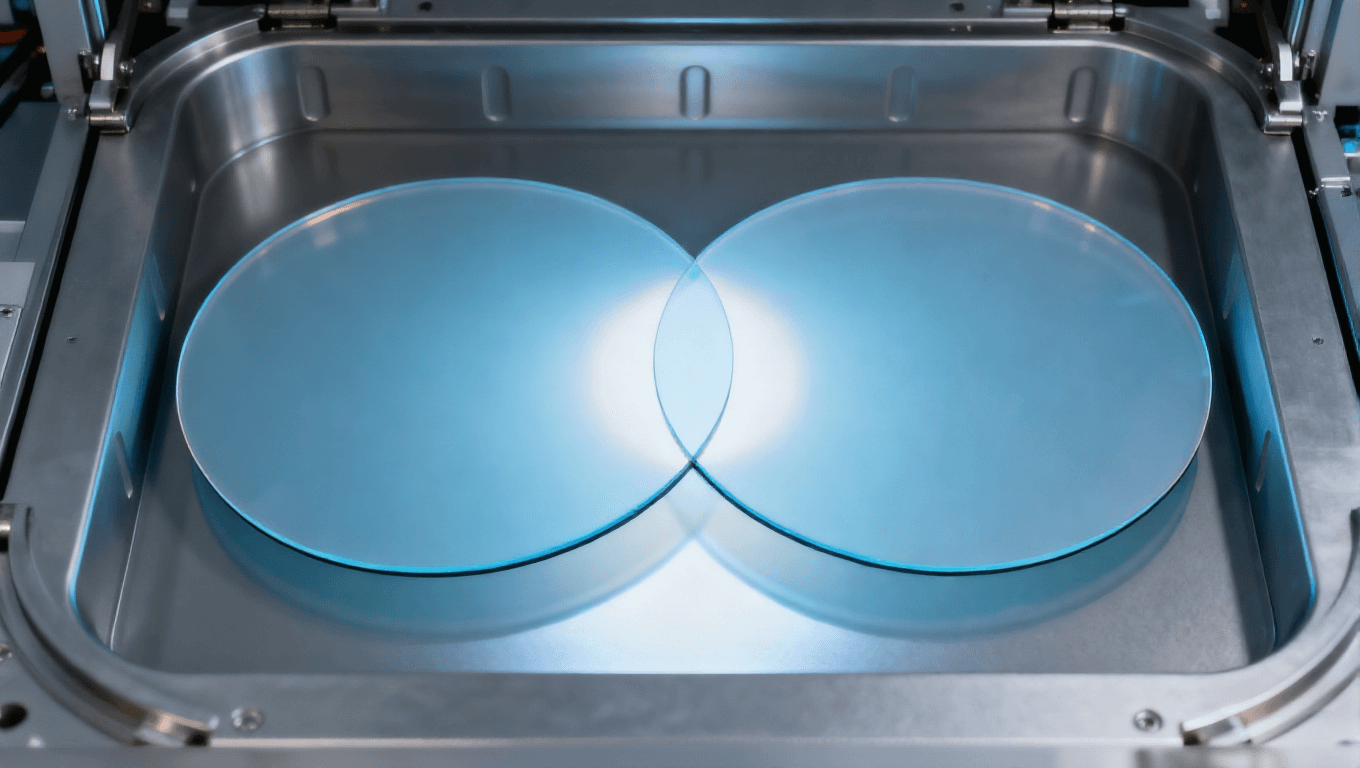

其次,硅通孔(TSV)技术是实现层间互连的核心手段。TSV是一种在硅基板上制作的垂直通道,内部填充导电材料(如铜),用于连接堆叠芯片的不同层。TSV的直径通常在几微米到几十微米之间,深度可达数百微米,其制造过程涉及深反应离子刻蚀、电镀和化学机械抛光等步骤。TSV技术的主要优势在于它提供了最短的互连路径,显著提升了信号传输速度。例如,在三维堆叠内存中,TSV可以将多个DRAM层连接起来,实现比传统二维封装更高的带宽和更低功耗。此外,TSV还能减少寄生电容和电感,进一步提高电路性能。

除了TSV,硅中介层是另一种常见的实现方式。硅中介层是一种位于堆叠芯片之间的薄硅片,上面布有互连线路,用于路由信号和电源。中介层可以通过TSV与上下芯片连接,形成一个完整的三维系统。这种方式特别适用于集成不同工艺节点的芯片,因为它提供了灵活的布线方案。例如,在高性能计算中,硅中介层可以将多个处理器和内存芯片集成在一起,实现高效的数据交换。

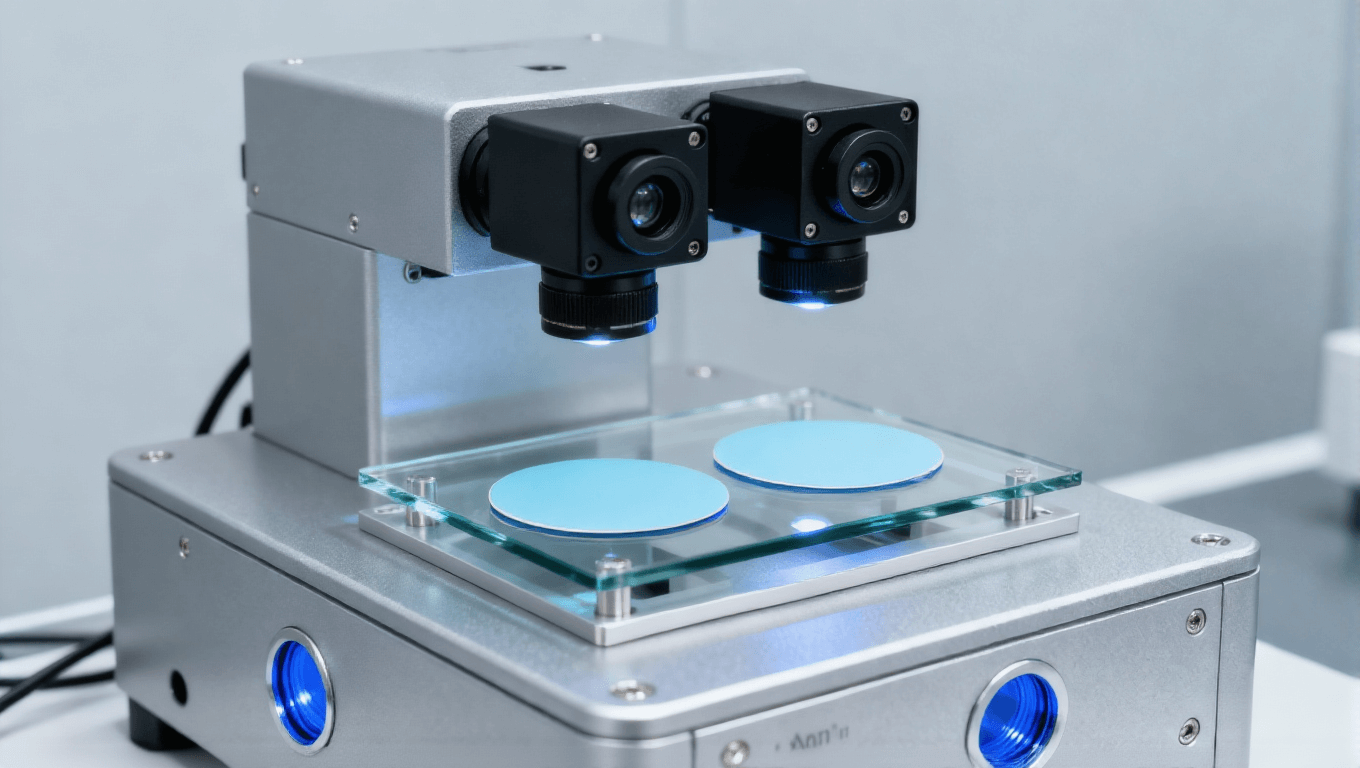

三维堆叠封装的实现还涉及多个工艺步骤,包括芯片减薄、对准键合和测试。芯片减薄是通过研磨或化学方法将芯片厚度降低到几十微米,以减少堆叠高度和改善热管理。对准键合则确保芯片在堆叠时精确对齐,常用方法包括热压键合和激光键合。测试环节在制造过程中至关重要,因为三维堆叠结构的复杂性使得故障检测和修复更具挑战性。总体而言,三维堆叠封装设计的实现依赖于多学科技术的融合,从材料工程到精密制造,每一步都需优化以确保可靠性和性能。

三、三维堆叠封装设计的优势与挑战

三维堆叠封装设计以其独特的垂直集成方式,带来了诸多优势,但也面临一系列技术挑战。理解这些优势与挑战,对于推动该技术的广泛应用至关重要。

优势方面,首先,三维堆叠封装显著提升了集成密度和性能。通过垂直堆叠,它可以在相同的占地面积内容纳更多芯片,从而实现更高的功能密度。这在移动设备和可穿戴设备中尤为重要,因为空间有限。例如,在智能手机中,三维堆叠封装可以将应用处理器、内存和射频芯片集成在一个模块中,减小主板尺寸并提升处理速度。其次,这种设计缩短了互连长度,降低了信号延迟和功耗。根据研究,三维堆叠封装的互连长度比二维封装缩短了50%以上,这使得数据传输速度更快,尤其在高速计算应用中,如人工智能和数据中心服务器。此外,三维堆叠封装支持异质集成,允许将不同工艺节点和材料的芯片组合在一起,优化系统性能。例如,将先进的逻辑芯片与成熟的存储芯片堆叠,可以降低成本并提高能效。最后,这种设计还提升了系统的可靠性和灵活性,因为它可以通过冗余设计减少单点故障,并适应多种应用场景。

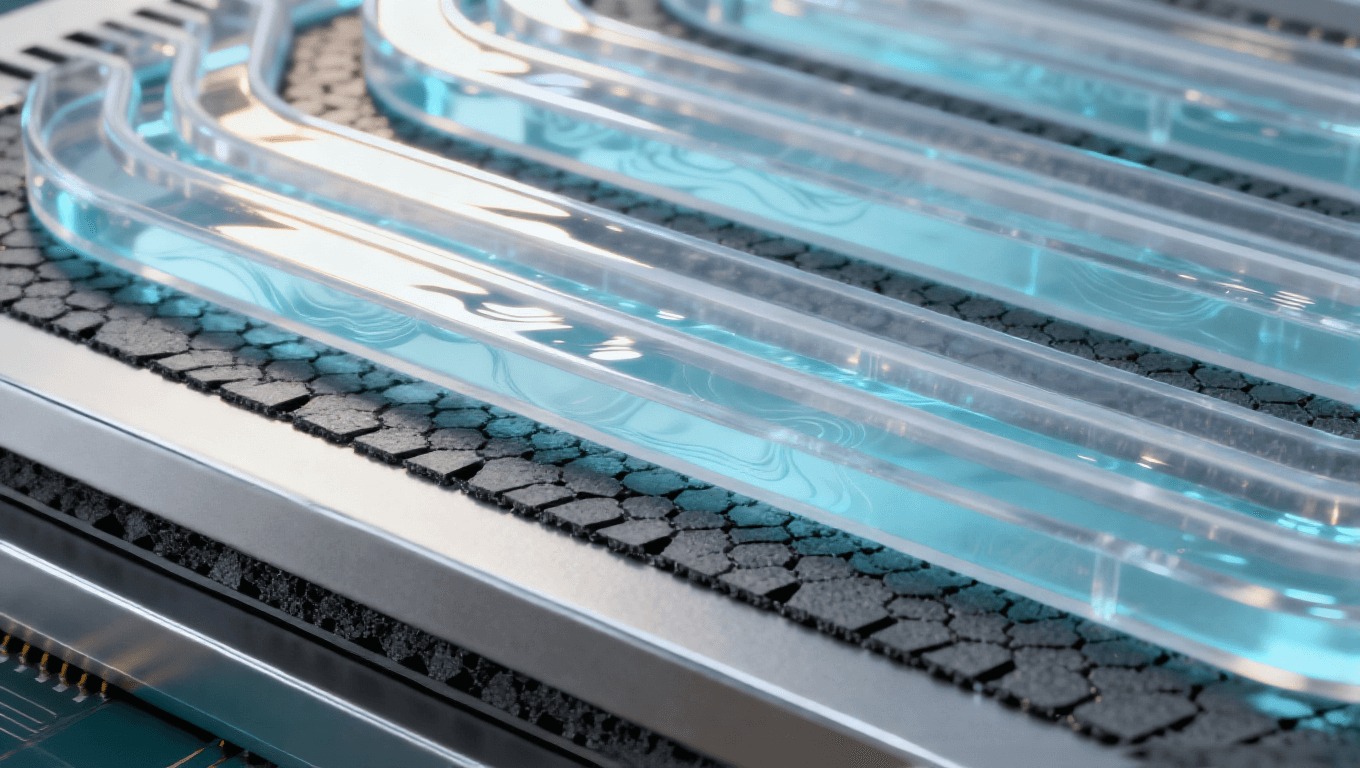

然而,三维堆叠封装设计也面临不少挑战。热管理是首要问题,因为堆叠结构会导致热量在垂直方向积聚,容易引发过热和性能下降。芯片之间的间隙小,散热路径有限,这就需要创新的热管理方案,如集成微流体冷却或使用高导热材料。另一个挑战是制造成本和工艺复杂性。三维堆叠涉及多个精密步骤,如TSV制造和芯片键合,这些过程需要高精度设备和高纯度材料,导致成本上升。据行业估计,三维堆叠封装的制造成本比传统封装高出30%-50%,这限制了其在低成本应用中的普及。此外,信号完整性和电源完整性也是关键问题。堆叠结构中的互连可能引入噪声和串扰,影响电路性能。设计时需采用屏蔽技术和优化布线来解决这些问题。

测试和可靠性同样是三维堆叠封装的挑战。由于堆叠结构复杂,传统测试方法可能无法全面检测故障,需要开发新的测试策略,如内置自测试(BIST)和三维扫描链。可靠性方面,堆叠芯片可能因热膨胀系数不匹配而产生机械应力,导致长期失效。因此,材料选择和结构设计需充分考虑耐久性。尽管存在这些挑战,但通过持续研发和跨行业合作,三维堆叠封装设计正逐步克服障碍,成为未来电子系统的关键。

四、三维堆叠封装设计的应用领域

三维堆叠封装设计因其高密度集成和性能优势,在多个领域得到广泛应用,从消费电子到高端计算,都展现出巨大潜力。以下是几个主要应用领域的详细分析。

在移动设备和消费电子领域,三维堆叠封装已成为提升设备性能的关键技术。智能手机、平板电脑和可穿戴设备需要小型化、高性能的芯片模块。例如,苹果的A系列芯片和三星的存储器模块采用三维堆叠设计,将处理器与内存堆叠在一起,实现更快的处理速度和更长的电池寿命。这种设计不仅减小了设备尺寸,还支持多功能集成,如将图像传感器与处理芯片堆叠,提升相机性能。在5G时代,三维堆叠封装还能集成射频前端模块,提高通信效率,满足高速数据传输需求。

高性能计算和人工智能是另一个重要应用领域。在这些应用中,数据处理速度和能效至关重要。三维堆叠封装允许将多个CPU、GPU和内存芯片堆叠在一起,形成高效的计算单元。例如,在服务器和超级计算机中,三维堆叠可以大幅提升并行处理能力,支持复杂的人工智能算法和机器学习任务。英伟达的GPU和英特尔的处理器已采用三维堆叠技术,通过TSV实现高带宽内存(HBM)集成,显著加速数据密集型应用。此外,在边缘计算中,三维堆叠封装帮助实现紧凑而强大的处理节点,适用于自动驾驶和工业物联网。

存储领域也广泛采用三维堆叠封装技术。NAND闪存和DRAM的内存堆叠已成为行业标准,通过垂直堆叠多个存储层,实现更高的容量和更快的读写速度。例如,三星和SK海力士的三维NAND闪存产品堆叠了数十甚至上百层,大幅提升了存储密度,同时降低了每比特成本。在固态硬盘(SSD)中,这种设计支持更高的IOPS(每秒输入输出操作数),满足大数据存储需求。此外,三维堆叠封装在传感器和MEMS(微机电系统)中也有应用,如将运动传感器与处理芯片堆叠,用于智能家居和医疗设备,实现实时数据采集和处理。

总之,三维堆叠封装设计的应用正不断扩展,推动电子设备向更智能、更高效的方向发展。随着技术的成熟,它有望在更多领域,如汽车电子和航空航天,发挥重要作用。

五、三维堆叠封装设计的未来发展趋势

三维堆叠封装设计作为半导体行业的前沿技术,其未来发展将受到多种趋势的驱动,包括材料创新、工艺优化和新应用拓展。预计在未来十年,这一技术将继续演进,带来更多突破。

首先,材料科学将是推动三维堆叠封装发展的关键因素。目前,硅基材料主导TSV和中介层技术,但研究人员正探索使用新型材料,如碳纳米管和石墨烯,以进一步提高导电性和热管理性能。这些材料具有更高的热导率和电导率,可以帮助解决堆叠结构中的散热问题。此外,先进封装材料如低介电常数(low-k)介质和高温粘合剂将提升互连可靠性和信号完整性。例如,开发柔性基板材料可能使三维堆叠封装适用于可弯曲电子设备,如柔性显示屏和可穿戴传感器。

其次,工艺优化和自动化将降低三维堆叠封装的制造成本并提高 (良率)。随着半导体设备精度的提升,TSV制造和芯片键合过程将变得更加高效和可靠。人工智能和机器学习技术在制造中的应用,可以实时监控工艺参数,预测故障,并优化生产流程。例如,通过AI驱动的检测系统,可以快速识别堆叠过程中的对准误差,减少废品率。同时,三维堆叠封装可能与其他先进封装技术融合,如扇出型封装(Fan-Out)和系统级封装(SiP),形成混合解决方案,以平衡性能和成本。据行业预测,到2030年,三维堆叠封装的成本可能下降20%-30%,使其在更广泛的市场中普及。

应用方面,三维堆叠封装将在新兴领域发挥更大作用。在量子计算中,这种设计可以用于堆叠量子比特芯片,实现更复杂的量子电路;在生物电子中,它可以集成传感器和处理单元,用于可植入医疗设备。此外,可持续发展趋势将推动三维堆叠封装向更环保的方向发展,例如使用可回收材料和低能耗制造工艺。总体而言,三维堆叠封装设计的未来充满机遇,它将与摩尔定律的延伸相辅相成,助力电子行业应对性能、尺寸和能效的挑战。

三维堆叠封装设计是半导体封装技术的一次重大革新,它通过垂直堆叠和高效互连,实现了高密度集成、性能提升和尺寸缩小。从技术原理到应用实践,这一设计展示了其在移动设备、高性能计算和存储领域的巨大价值。尽管面临热管理、制造成本和可靠性等挑战,但通过持续创新,这些障碍正逐步被克服。未来,随着材料、工艺和应用的不断拓展,三维堆叠封装设计有望成为电子系统的核心,推动行业向更智能、更可持续的方向发展。