一、高多层 PCB 打样:定义与行业核心价值

高多层 PCB 通常指层数在 8 层及以上的印制电路板,其打样环节是产品研发阶段的关键步骤 —— 通过小批量试产验证设计方案可行性、工艺适配性与性能稳定性。不同于普通 PCB 打样,高多层 PCB 打样面临层数叠加带来的信号完整性、结构稳定性、工艺兼容性等多重挑战,其质量直接决定研发周期、生产成本与最终产品竞争力。

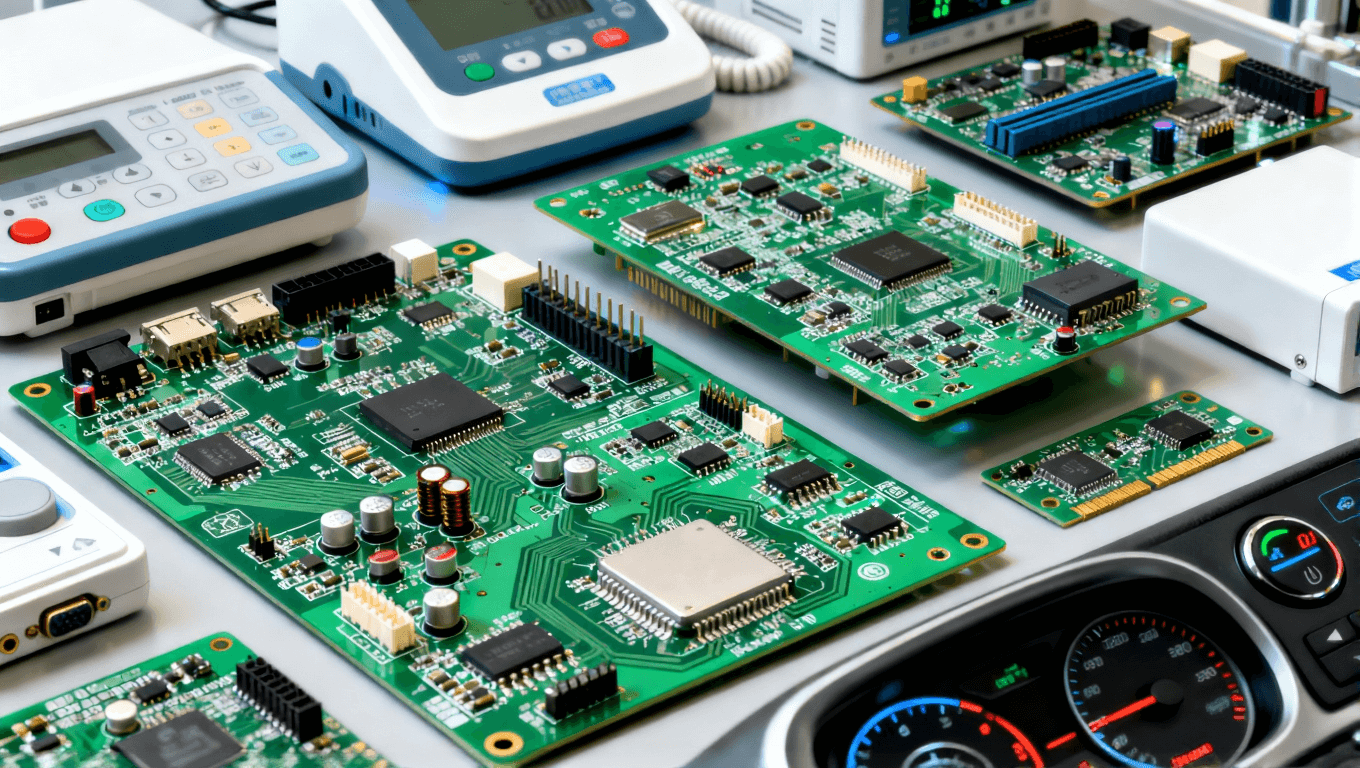

在电子制造行业,高多层 PCB 打样的价值早已超越 “样品验证” 本身。对于工业控制设备,它是保障复杂指令精准传输的基础;对于医疗电子器械,它是实现高精度传感与数据处理的核心载体;对于新能源汽车,它是支撑车载系统高集成度、高可靠性运行的关键部件。尤其是在 5G、人工智能、物联网等技术推动下,电子设备对 PCB 的密度、层数、性能要求持续提升,高多层 PCB 打样的技术门槛与行业价值同步凸显,成为企业抢占市场先机的重要环节。

二、高多层 PCB 打样的关键技术要点

高多层PCB打样的技术核心在于解决 “多层叠加” 带来的一系列问题,从层间连接到信号传输,每一个环节的精准控制都直接影响样品质量。

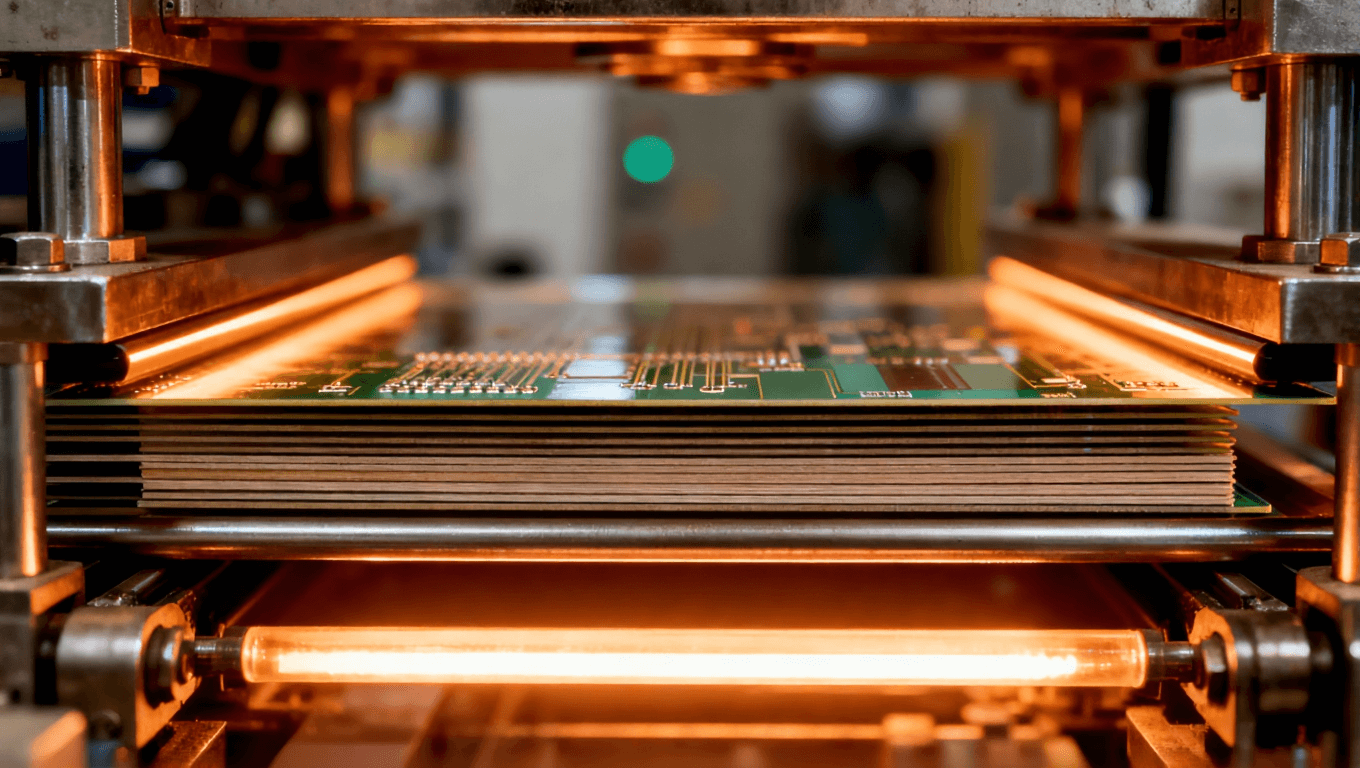

1. 层压工艺:多层结构的 “无缝衔接”

层压是高多层 PCB 打样的核心工序,其核心目标是将多层芯板、半固化片(PP 片)精准压合为一个整体,同时保证层间对齐精度与粘结强度。

• 对齐精度控制:高多层 PCB 层数多、厚度大,层间偏移误差需控制在 ±0.1mm 以内,通常采用销钉定位或光学定位技术,搭配高精度层压机实现精准对齐,避免因偏移导致过孔连接失效。

• 压力与温度曲线优化:根据芯板材料(如 FR-4、高频材料)与半固化片型号,定制专属压力 - 温度曲线。升温阶段需缓慢均匀,避免芯板与 PP 片热膨胀系数差异导致的分层;加压阶段需逐步提升压力,确保层间无气泡、无空洞,粘结强度达标。

• 厚度均匀性把控:通过控制芯板厚度公差、PP 片铺层数量与压力分布,保证压合后 PCB 总厚度公差在 ±10% 以内,避免因厚度不均影响后续钻孔、阻焊等工序。

2. 钻孔技术:多层导通的 “精准通道”

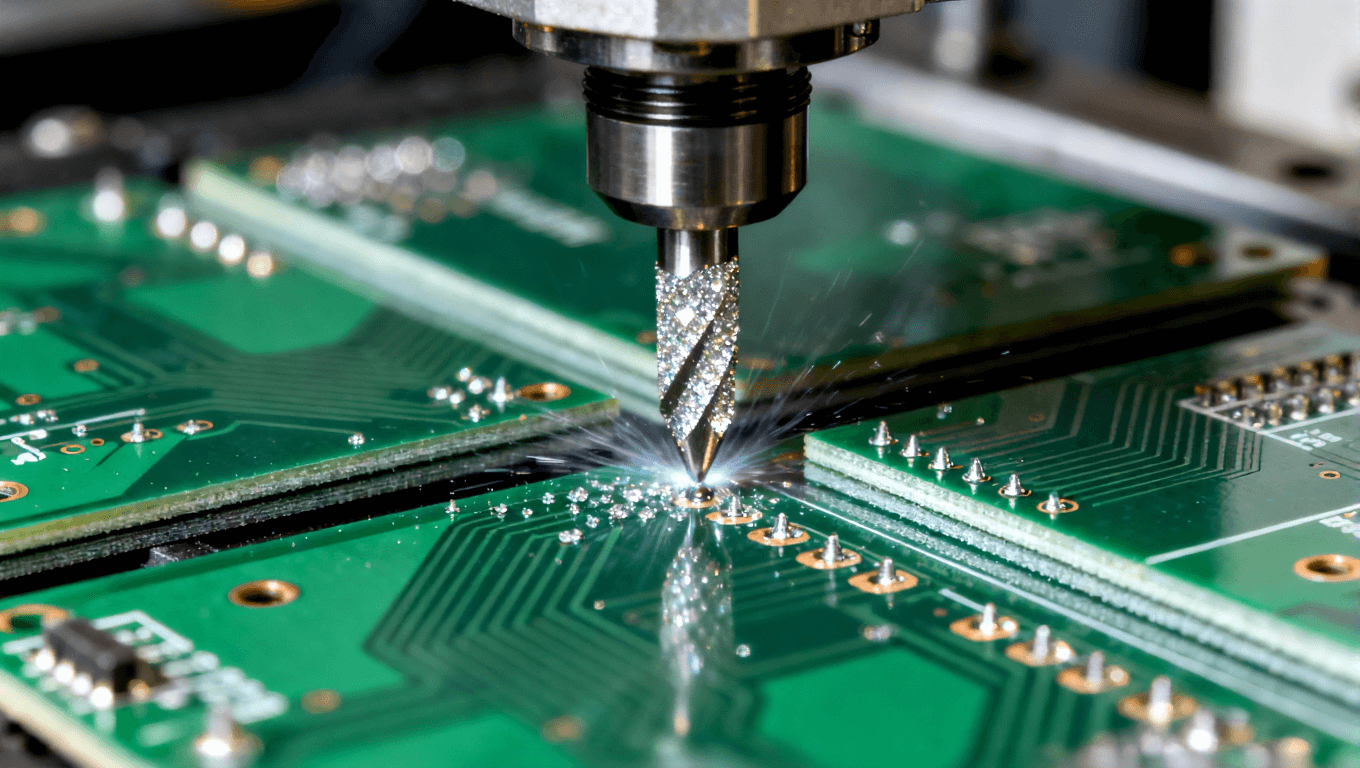

高多层 PCB 的过孔是实现层间信号与电源导通的关键,钻孔质量直接影响电气性能与机械可靠性,其技术难点集中在微小孔径、深径比控制与毛刺处理。

• 微小孔径加工:工业级高多层 PCB 打样常涉及 0.2mm 以下的微小过孔,需选用金刚石涂层钻头或 carbide 钻头,搭配高速钻机(转速≥10 万转 / 分钟),同时控制进给速度,避免钻头折断或孔壁粗糙。

• 深径比控制:高多层 PCB 厚度大,过孔深径比常达到 6:1 以上,需通过优化钻头几何参数、采用分步钻孔工艺,减少孔壁撕裂与铜层脱落风险,保证孔内电镀均匀性。

• 毛刺清除:钻孔后孔口易产生毛刺,需通过化学去毛刺或机械去毛刺工艺处理,尤其针对内层铜箔,避免毛刺导致层间短路,确保样品电气性能稳定。

3. 阻抗控制:信号传输的 “稳定保障”

高多层 PCB 多用于高频、高速信号传输场景,阻抗不匹配会导致信号反射、衰减,影响设备正常工作,因此阻抗控制是打样阶段的核心技术要求。

• 阻抗计算与设计:根据产品需求(如 50Ω、100Ω 差分阻抗),结合 PCB 材料介电常数、铜箔厚度、线宽、线距等参数,通过专业阻抗计算软件(如 Polar SI9000)进行精准设计,预留阻抗调整余量。

• 工艺参数把控:在蚀刻工序中,控制蚀刻液浓度、温度与蚀刻时间,保证线宽公差在 ±0.03mm 以内,避免线宽偏差导致阻抗漂移;对于微带线、带状线等不同布线结构,针对性调整层间介质厚度,确保阻抗值符合设计要求。

• 阻抗测试与校准:打样完成后,采用阻抗测试仪对关键信号线路进行逐点测试,若阻抗偏差超出允许范围,通过调整线宽或介质厚度进行校准,确保样品满足高频信号传输需求。

三、高多层 PCB 打样的全流程工艺把控

高多层 PCB 打样是一个系统工程,从设计优化到交付检测,每个环节都需建立严格的工艺标准,确保样品质量稳定、可复制。

1. 设计阶段:DFM 优化适配打样工艺

面向制造的设计(DFM)是高多层 PCB 打样成功的前提,通过设计优化减少工艺难度,降低试产风险。

• 布线优化:避免在高密度区域设置过长的平行走线,减少信号串扰;关键信号线路采用差分走线设计,提升抗干扰能力;预留足够的测试点,方便后续电气性能检测。

• 过孔设计:合理选择过孔类型(如盲孔、埋孔、通孔),盲孔与埋孔可减少信号传输路径,降低损耗,同时减少 PCB 表面占用空间;过孔间距需大于 2 倍孔径,避免钻孔时相互影响。

• 热设计考量:高多层 PCB 散热难度大,设计时需预留散热通孔或散热铜皮,避免大功率器件区域因热量积聚导致 PCB 变形或性能衰减。

2. 材料选型:匹配性能与工艺需求

材料选择直接影响高多层 PCB 打样的性能、成本与工艺兼容性,需根据产品应用场景精准选型。

• 基材选择:普通工业级产品可选用标准 FR-4 基材(介电常数 4.2-4.6),高频场景(如 5G 设备)需选用高频基材(如 PTFE、罗杰斯系列,介电常数 2.2-3.0),医疗电子、汽车电子等高温场景需选用耐高温基材(玻璃化温度 Tg≥170℃)。

• 铜箔选择:内层铜箔常用 1oz(35μm)或 2oz(70μm),外层铜箔可根据电流需求选择 1oz-3oz;高频信号线路建议选用电解铜箔,提升信号传输稳定性。

• 半固化片选择:根据芯板厚度与压合要求,选择合适型号的 PP 片(如 1080、2116),确保其流动度、凝胶时间与芯板适配,避免压合时出现溢胶或粘结不牢。

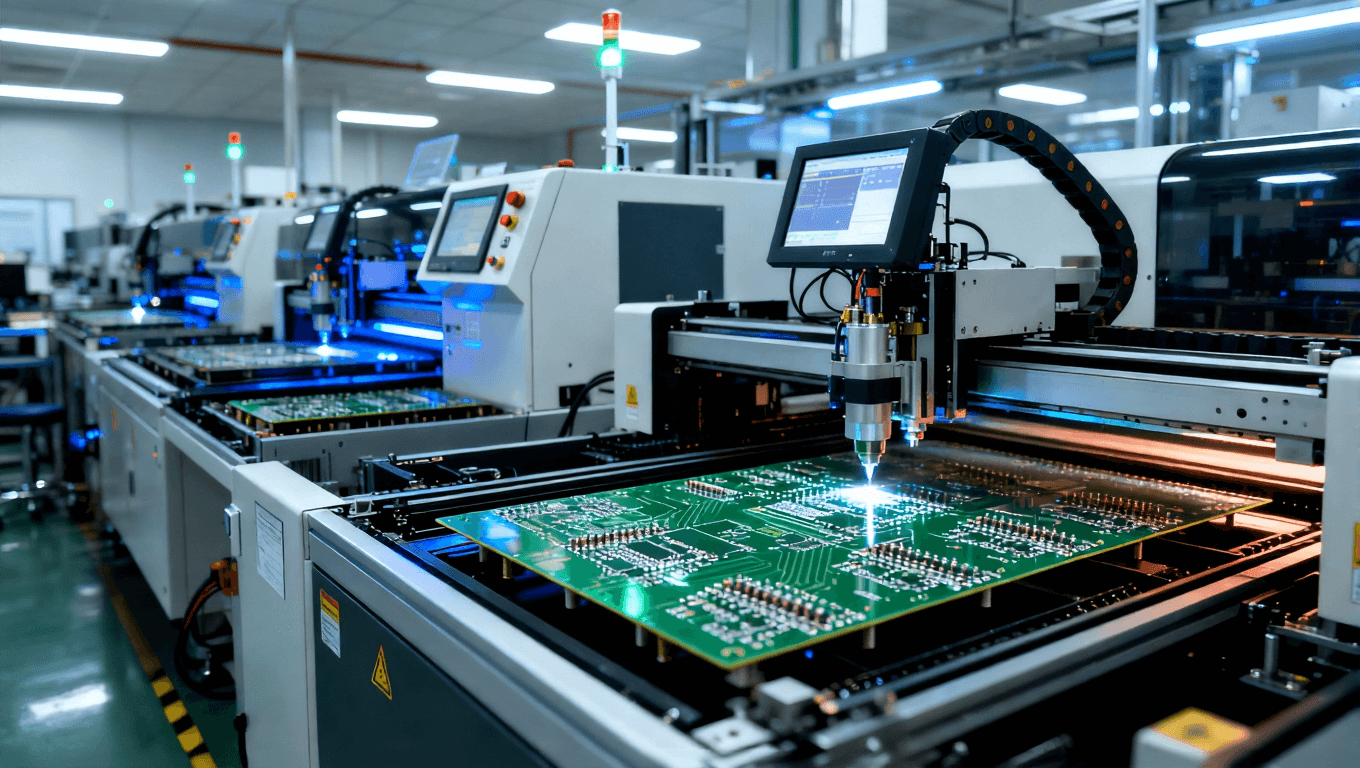

3. 生产阶段:关键工序质量管控

高多层 PCB 打样的生产过程需建立多道质量检测节点,及时发现并解决工艺问题。

• 内层图形转移:采用高精度曝光机(曝光精度≤±0.02mm),确保内层线路图形清晰、无变形;显影后通过 AOI(自动光学检测)设备检测线路缺陷,如开路、短路、线宽偏差等,及时返修。

• 电镀工艺:孔内电镀采用垂直电镀线,控制电流密度、电镀时间与镀液浓度,保证孔内铜层厚度均匀(通常≥20μm),避免出现孔壁镀铜不足或空洞;表面处理可根据需求选择喷锡、沉金、OSP 等工艺,提升焊接可靠性与抗氧化能力。

• 阻焊与丝印:阻焊油墨需选用耐高温、耐化学腐蚀的型号,曝光时确保阻焊开窗精准,避免遮挡焊盘;丝印时控制油墨厚度,保证字符清晰、不易脱落,便于后续装配与维修。

4. 检测阶段:全面验证样品质量

高多层 PCB 打样完成后,需通过多维度检测验证其性能与可靠性,确保满足设计要求。

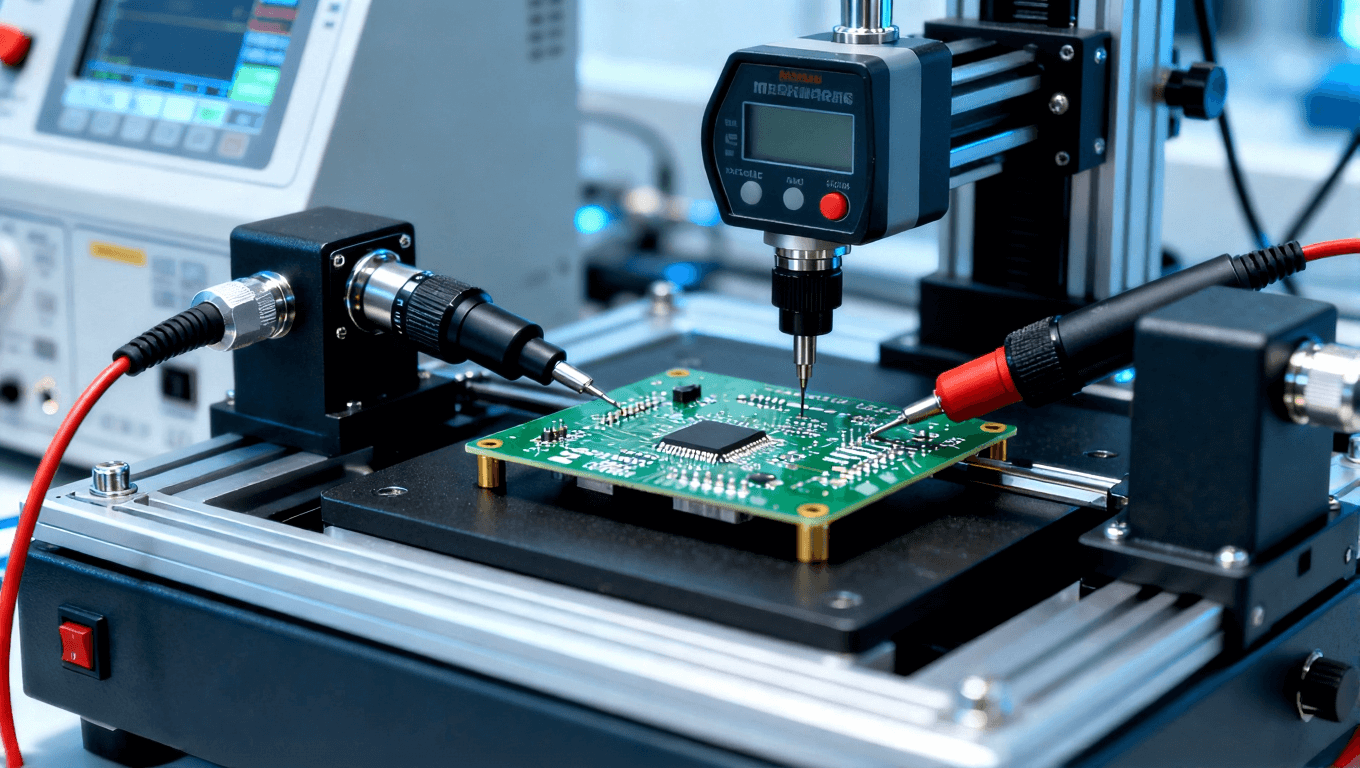

• 电气性能检测:采用飞针测试机对所有网络进行导通性与绝缘性测试,排查开路、短路等问题;通过阻抗测试仪验证关键线路阻抗值,确保信号传输稳定。

• 物理性能检测:检测 PCB 厚度、线宽、孔径等关键尺寸,验证是否符合设计公差;通过热冲击测试(-40℃~125℃,循环 50 次)与湿热测试,评估样品环境适应性;采用 X 光检测设备检查层间对齐精度与过孔电镀质量,避免分层、气泡等隐性缺陷。

• 可靠性测试:对于汽车电子、医疗电子等高端应用场景,还需进行焊接可靠性测试、盐雾测试等,确保样品在恶劣环境下长期稳定工作。

四、高多层 PCB 打样的行业应用场景与实战案例

高多层 PCB 打样的技术要求与工艺标准,需结合具体行业应用场景进行定制化调整,不同领域的产品对样品性能的侧重点存在显著差异。

1. 工业控制领域:高稳定性与抗干扰性

工业控制设备(如 PLC、变频器、伺服控制器)需在复杂工业环境中长期稳定运行,高多层 PCB 打样需重点关注抗干扰性与机械可靠性。

• 实战案例:某工业控制企业研发高精度变频器,需 8 层 PCB 打样。针对工业现场强电磁干扰问题,打样时采用差分走线设计,内层设置接地屏蔽层;选用 Tg=180℃的耐高温 FR-4 基材,提升环境适应性;通过优化层压工艺,将层间对齐精度控制在 ±0.08mm 以内,确保过孔导通稳定。样品经测试,电磁兼容性(EMC)达标,在 - 20℃~85℃环境下连续运行 72 小时无故障,成功通过研发验证。

2. 医疗电子领域:高精度与生物兼容性

医疗电子器械(如心电图机、超声诊断仪、血糖仪)对信号检测精度与安全性要求极高,高多层 PCB 打样需兼顾电气性能与生物兼容性。

• 实战案例:某医疗设备公司研发便携式超声诊断仪,需 12 层 PCB 打样。为实现高精度超声信号处理,选用高频 FR-4 基材(介电常数 4.3),优化阻抗控制工艺,将差分阻抗偏差控制在 ±5% 以内;表面处理采用沉金工艺,提升焊接可靠性与生物兼容性;打样过程中严格控制 PCB 翘曲度(≤0.5%),避免影响设备内部装配精度。样品经临床测试,信号检测精度达到 0.1mV,满足医疗设备行业标准,顺利进入量产阶段。

3. 汽车电子领域:高耐温与抗震性

车载电子设备(如车载导航、自动驾驶控制器、电池管理系统 BMS)需承受高温、振动等恶劣环境,高多层 PCB 打样需重点强化可靠性与耐久性。

• 实战案例:某新能源汽车企业研发自动驾驶控制器,需 16 层 PCB 打样。针对车载环境高温特性,选用 Tg=200℃的高耐热基材,搭配无卤阻燃 PP 片,提升防火安全性;采用盲埋孔设计,减少 PCB 体积与重量,同时提升信号传输速度;打样后通过振动测试(10Hz~2000Hz,加速度 20g)与长时间高温老化测试(125℃,连续 1000 小时),样品无分层、无短路,满足车载电子可靠性标准,成功应用于原型车测试。

4. 消费电子领域:高集成度与小型化

消费电子设备(如高端智能手机、平板电脑、VR 设备)追求小型化、轻薄化与高集成度,高多层 PCB 打样需重点关注高密度布线与空间利用率。

• 实战案例:某消费电子企业研发高端 VR 头显,需 10 层 PCB 打样。为实现高集成度设计,采用微过孔(孔径 0.15mm)与高密度布线(线宽 / 线距 = 0.1mm/0.1mm);选用薄型 FR-4 基材(芯板厚度 0.1mm),搭配 1080 型薄 PP 片,将 PCB 总厚度控制在 1.2mm 以内;通过 DFM 优化,避免布线交叉干扰,提升信号传输效率。样品经测试,信号延迟≤5ns,满足 VR 设备高速数据处理需求,成功适配产品轻薄化设计。

五、高多层 PCB 打样的选型误区与避坑指南

在高多层 PCB 打样过程中,企业常因选型不当、工艺认知不足等问题导致研发周期延长、成本增加,以下是常见误区与规避方法。

1. 误区一:盲目追求高层数,忽视实际需求

部分企业认为层数越多,PCB 性能越好,盲目选择 16 层、20 层等高层数打样,导致成本大幅增加,且工艺难度提升。

• 避坑指南:根据产品功能需求与信号复杂度确定层数,通过合理的布线优化与层叠设计,在满足性能要求的前提下,尽量减少层数。例如,10 层 PCB 可实现的功能,无需盲目选择 12 层,避免资源浪费。

2. 误区二:忽视 DFM 优化,导致打样失败

部分企业在设计阶段未考虑打样工艺可行性,导致 PCB 设计文件与生产工艺不匹配,出现无法加工或样品性能不达标等问题。

• 避坑指南:打样前与 PCB 厂家工程师沟通,进行 DFM 优化。重点关注线宽、孔径、过孔间距等关键参数是否符合工艺能力,避免设计出超出生产极限的结构;提前明确基材、表面处理等工艺要求,确保设计方案与生产能力匹配。

3. 误区三:只关注价格,忽视厂家技术实力

部分企业选择 PCB 打样厂家时,仅以价格为核心考量因素,忽视厂家的技术实力、工艺水平与质量管控能力。

• 避坑指南:选择具备高多层 PCB 打样经验的厂家,重点考察其设备水平(如高精度钻机、层压机、检测设备)、技术团队与行业案例;要求厂家提供样品检测报告,验证其工艺稳定性;优先选择可提供定制化服务的厂家,确保能够根据产品需求调整工艺方案。

4. 误区四:材料选型不当,影响样品性能

部分企业在材料选型时,未结合产品应用场景,盲目选择高端材料或低价材料,导致样品性能不达标或成本过高。

• 避坑指南:根据产品应用环境(温度、湿度、电磁干扰)与性能要求,精准选择基材、铜箔、半固化片等材料。例如,普通消费电子可选用标准 FR-4 基材,高频场景需选用专用高频基材;避免为降低成本选择低质量材料,同时也无需过度追求高端材料,实现性能与成本的平衡。

六、高多层 PCB 打样的技术趋势与未来展望

随着电子技术的持续迭代,高多层 PCB 打样正朝着高密度、高频化、绿色化、智能化方向发展,技术创新与工艺升级成为行业核心竞争力。

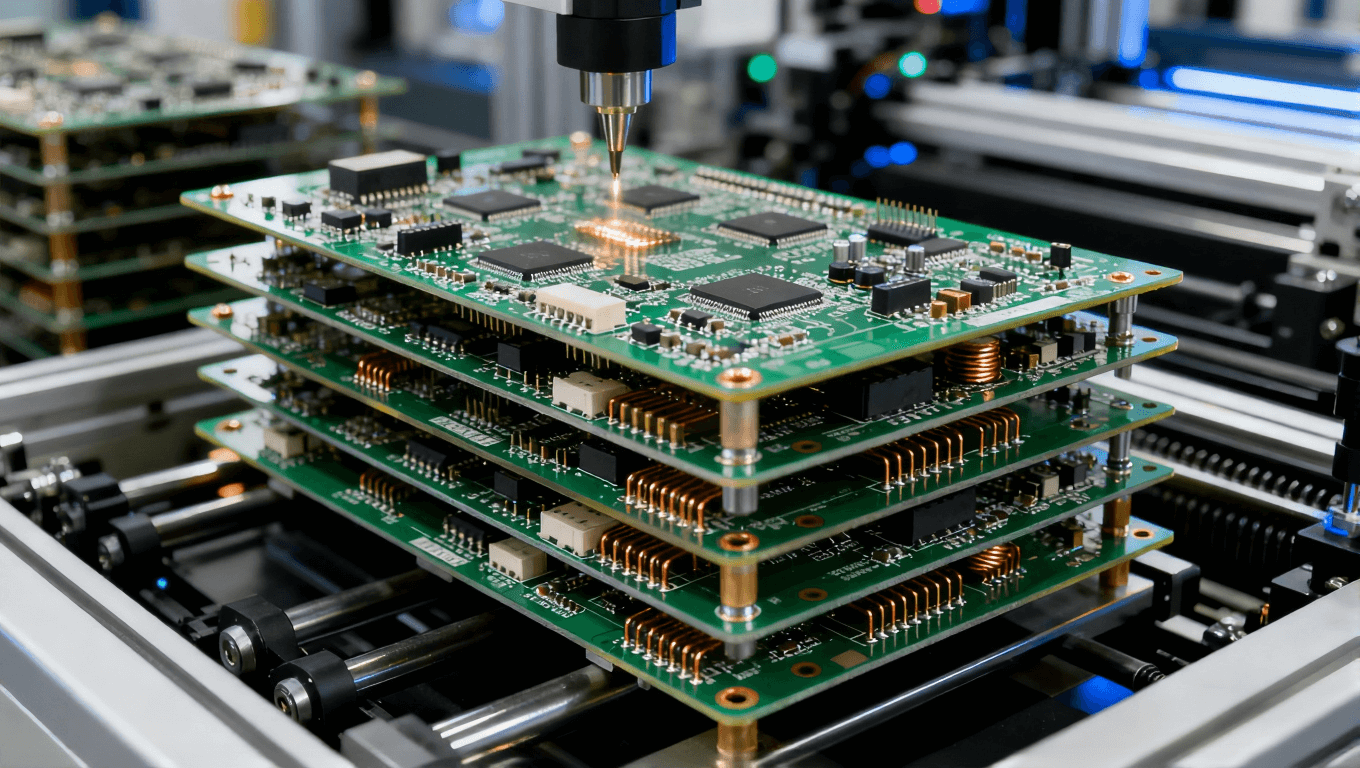

1. 高密度化:微过孔与埋盲孔技术普及

为满足电子设备小型化、高集成度需求,高多层 PCB 打样将广泛采用微过孔(孔径≤0.1mm)与埋盲孔技术,减少 PCB 体积与重量,提升布线密度。同时,HDI(高密度互连)技术的应用将进一步提升信号传输速度与稳定性,成为高端产品打样的主流选择。

2. 高频化:高频材料与工艺优化

5G、人工智能等技术的发展,推动电子设备信号频率持续提升,高多层 PCB 打样需适配高频信号传输需求。未来,高频基材(如 PTFE、液晶聚合物 LCP)的应用将更加广泛,阻抗控制工艺将更加精准,通过优化布线结构与材料组合,降低信号衰减与串扰。

3. 绿色化:环保材料与工艺推广

在全球环保政策趋严的背景下,高多层 PCB 打样将逐步采用无卤、低铅、环保型材料,推广节能减排的生产工艺(如无铅电镀、水性阻焊油墨)。同时,PCB 厂家将加强废弃物回收利用,降低生产过程对环境的影响,实现绿色制造。

4. 智能化:数字化与自动化升级

高多层 PCB 打样将引入更多智能化技术,如数字化设计与仿真软件的普及,可提前预判工艺风险;自动化生产设备(如全自动层压机、智能检测设备)的应用,将提升生产效率与产品一致性;大数据与物联网技术的融合,可实现打样全流程的实时监控与质量追溯,进一步保障样品质量。

结语

高多层 PCB 打样是电子产品研发的关键环节,其技术核心在于精准把控层压、钻孔、阻抗控制等关键工序,工艺重点在于结合行业应用场景进行定制化设计与全流程质量管控。随着电子技术的不断发展,高多层 PCB 打样的技术门槛将持续提升,企业需选择具备技术实力与行业经验的高多层板打样厂家,通过科学的选型、优化的设计与严格的检测,确保样品质量达标,为产品量产奠定坚实基础。了解更多详情欢迎联系爱彼电路技术团队