陶瓷基板线路设计的核心参数是线宽与线距。这两个数值直接限制了基板的电气性能、热管理能力和集成密度。在高功率、高频率、高可靠性应用中,线宽线距的每微米偏差都可能导致温升超标、击穿失效或信号失真。不同金属化工艺对线宽线距的实现能力差异显著,工程师必须根据具体应用场景选择合适的工艺路线和参数范围。本文系统梳理主流工艺的精度边界、设计约束与优化策略,为实际项目提供参考依据。

陶瓷板以氧化铝、氮化铝或氮化硅等材料为基体,通过金属化形成铜线路或其他导电层。相比有机PCB,陶瓷板导热系数高出10-50倍,热膨胀系数更接近半导体芯片,因此成为第三代半导体功率模块和射频器件的首选载体。然而,陶瓷材料的硬脆特性和高温加工要求,使得线宽线距的控制难度远高于普通PCB。线宽主要影响电流承载与阻抗,线距则主导绝缘强度与串扰抑制,二者共同决定基板能否在极端环境下稳定工作。

线宽线距参数对性能的直接影响

线宽决定了线路截面积,从而影响电阻、发热和载流能力。相同铜厚下,线宽每减半,电阻约增大一倍,温升随之显著上升。陶瓷板虽导热优秀,但局部热斑仍会加速焊层老化或引起芯片失效。

线距决定了相邻线路间的电气间隙与电磁耦合程度。在高压应用中,线距不足会导致沿面闪络或局部放电;在高频应用中,线距过小会增加寄生电容与互感,破坏信号完整性。此外,制造过程的侧蚀、翘曲和对准误差都会使实际线宽线距偏离设计值,因此设计阶段必须预留足够裕量。

以典型1200V/400A SiC功率模块为例,基板需同时满足大电流、低寄生参数和150℃以上高温要求。线宽通常设定在0.3-0.5mm以控制温升,线距则需≥0.4mm以保证耐压余量。若采用更精细工艺将线宽线距压缩至0.1mm以下,则可显著提升功率密度,但对制造一致性提出更高挑战。

四大金属化工艺的线宽线距能力详解

当前陶瓷板主流工艺包括DBC、DPC、薄膜和厚膜,四者在精度、载流、成本和可靠性上形成明显梯度。

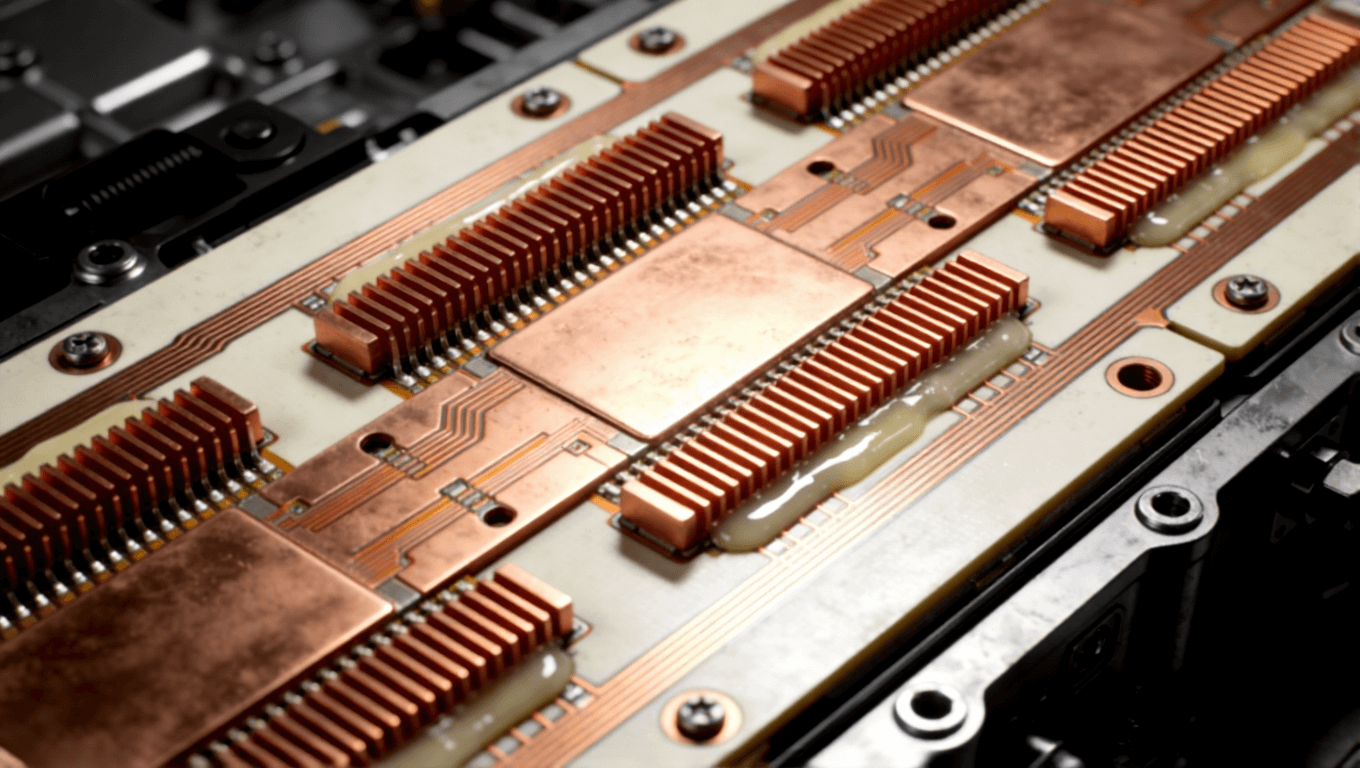

1. DBC(直接键合铜)工艺

通过高温共晶反应将厚铜箔(200-400μm)直接键合到陶瓷表面,再经蚀刻形成线路。

线宽线距要求:批量生产最小0.12mm(铜厚300μm时),打样可达0.10mm,公差±15μm。

DBC的最大优势是载流与散热能力,一条0.4mm宽线路可连续承载180A以上电流,热阻极低。主要用于新能源汽车主驱逆变器、轨道交通变流器等大功率场景。实际量产数据显示,DBC基板在3000小时双85测试后线路完整率接近100%。

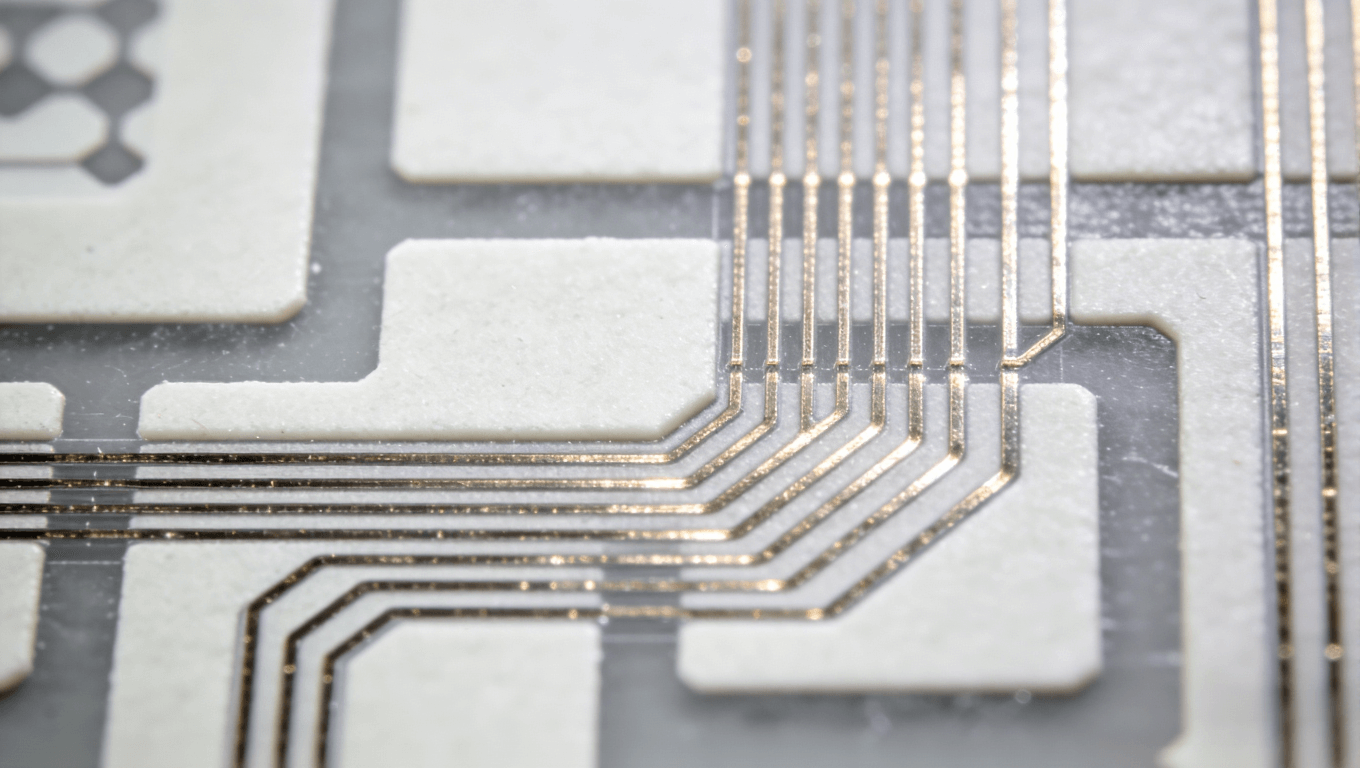

2. DPC(直接镀铜)工艺

采用溅射种子层、光刻显影、电镀加厚相结合,实现精细图形与中等铜厚(10-100μm)。

线宽线距要求:常规批产60-80μm,高精度产线稳定40-50μm,对准精度±2μm,侧壁垂直度>85°。

DPC在精度与成本间取得最佳平衡,已广泛应用于5G基站射频模块、MiniLED背光源等中高端领域。某知名企业采用氮化铝DPC基板,将线宽线距控制在50μm,成功实现28GHz功率放大器阻抗精确匹配,插入损耗较传统方案降低15%。

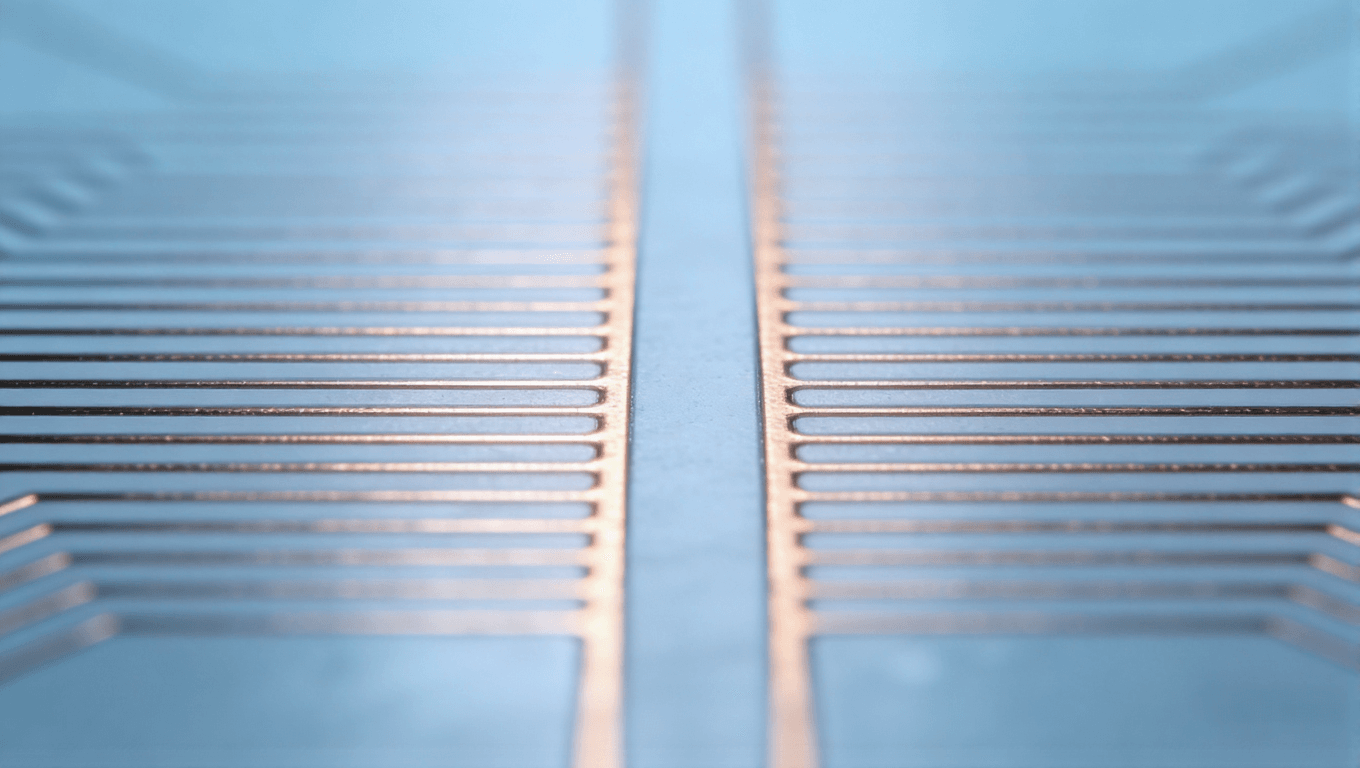

3. 薄膜(TFC)工艺

真空溅射多层金属(Ti/Cu/Ni/Au等),厚度通常1-5μm,光刻精度最高。

线宽线距要求:标准20-30μm,最小可稳定10μm以下,公差±1μm。

薄膜工艺寄生参数极低,适合微波集成电路、LD/VCSEL光模块等高频小信号场景。但载流能力有限,通常需配合局部加厚或外部引线框使用。

4. 厚膜(TPC)工艺

丝网印刷银/铜浆料后高温烧结形成线路,厚度20-50μm。

线宽线距要求:常规150-250μm,极限可达80-100μm。

成本最低,工艺成熟,适合普通LED驱动、工业传感器等对精度要求不高的批量应用。尽管线宽线距较粗,但耐环境应力能力突出,常用于苛刻工况下的低成本方案。

设计阶段的五大关键约束与优化方法

确定工艺后,具体线宽线距数值需综合多因素迭代计算。

• 载流与热管理:参考IPC-2152修正模型,结合陶瓷导热系数,可允许更高电流密度。例如,2oz铜厚线路承载30A时,线宽仅需0.3mm即可将温升控制在15℃以内。

• 耐压与电气间隙:依据IEC 60950或AEC-Q101标准,1000V以上应用需线距≥1.0-1.5mm。陶瓷表面光洁度高,可适当减小间隙,但需通过HiPot与偏压湿热测试验证。

• 信号完整性:高频设计需使用Ansys HFSS或Keysight ADS仿真微带/共面结构。典型50Ω微带线在氮化铝基板上,线宽约0.16mm、线距0.20mm即可实现回波损耗<-20dB。

• 热机械可靠性:铜与陶瓷CTE差异导致热应力,过细线路在-55~200℃温冲中易开裂。DBC建议线宽≥0.2mm并采用大圆角过渡,DPC则需控制铜厚≤50μm以降低翘曲。

• 制造公差与良率:精密线路需考虑蚀刻侧腐(约10-20μm)和对准偏差。目标50μm线宽时,设计值推荐60μm,确保批产良率>98%。

典型失效案例与参数优化实践

案例一

某企业早期SiC模块采用DBC基板,设计线宽线距0.15mm。高压高温反偏(H3TRB)测试中出现击穿。失效分析显示,蚀刻侧腐导致实际线距缩小至0.12mm,电场集中超标。优化后将线距增大至0.25mm并添加边缘钝化,最终通过AEC-Q104认证,模块寿命提升至原先的4倍。

案例二

MicroLED驱动基板原使用厚膜工艺,线宽线距180μm限制像素密度。切换DPC后压缩至45μm,像素间距缩小40%,亮度均匀性提升18%,整体模组功耗降低12%,成功实现量产。

未来发展方向:极致精度与复合工艺

随着GaN/SiC器件向更高频率、更小封装演进,陶瓷板线宽线距要求正向20μm甚至5μm级推进。激光辅助蚀刻、EUV光刻移植、纳米压印等新技术已进入工程验证阶段。同时,DPC+局部DBC复合工艺将成为主流,实现“精细信号线+大电流功率线”一体化。

数字孪生平台与AI优化工具也正在改变设计流程。通过多物理场耦合仿真与机器学习,工程师可在布局阶段快速收敛最优线宽线距组合,显著缩短开发周期并提升一次成功率。

线宽线距要求是陶瓷板技术的核心门槛,直接决定产品在功率密度、可靠性和成本上的竞争力。深入理解不同工艺边界与设计约束,才能在实际项目中实现性能与制造性的最佳平衡。