你是否曾经在深夜调试一块PCB,却被莫名其妙的信号抖动折磨得头疼?示波器上那细微却顽固的电源纹波,像隐形敌人一样破坏了整个系统的稳定性。很多工程师第一时间怀疑是代码问题或芯片缺陷,但真相往往藏在一个容易被忽略的细节——电源去耦策略不到位。

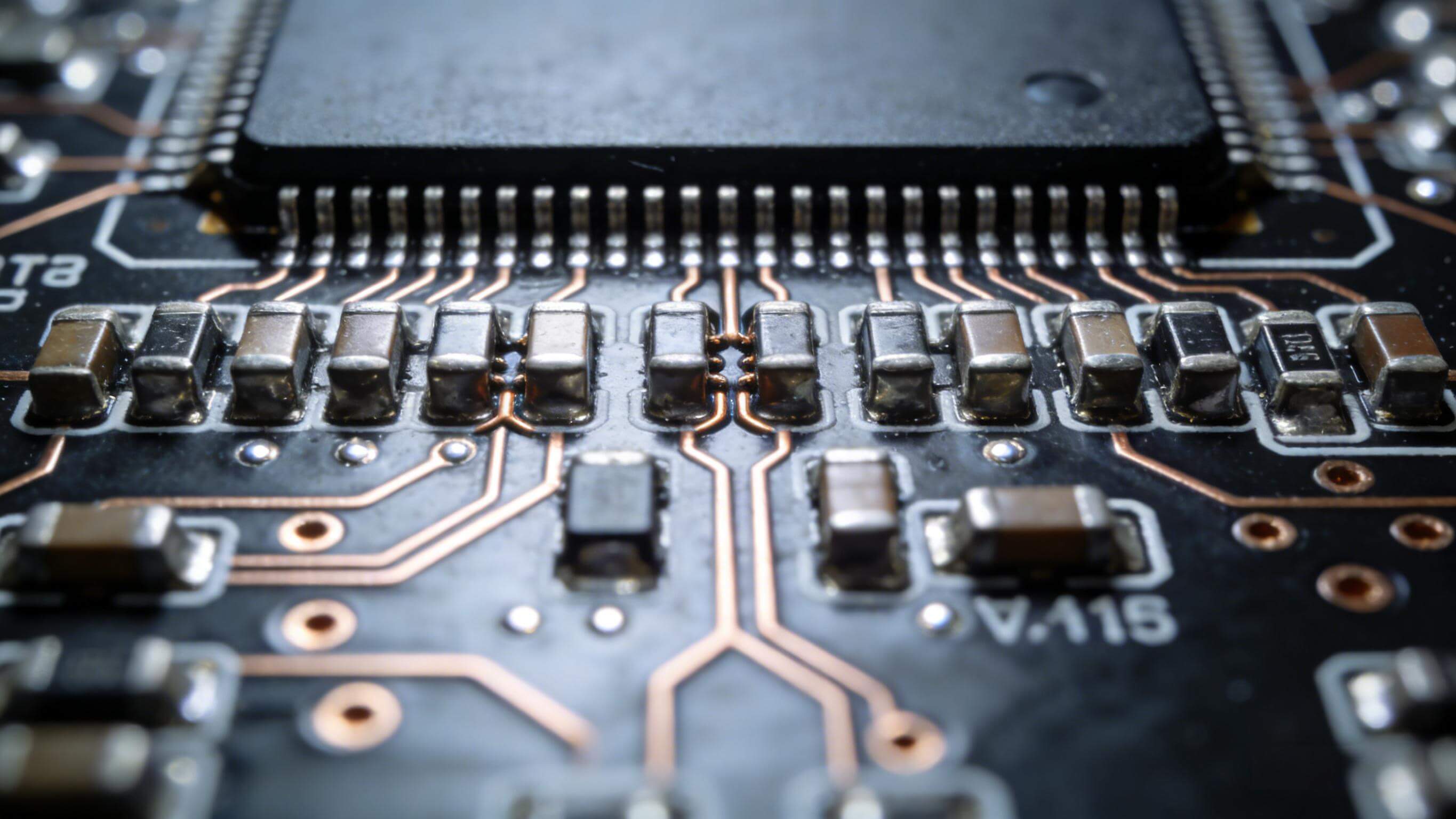

电源噪声并非抽象概念,它直接决定高速数字电路能否可靠运行。当IC在纳秒级切换状态时,会从电源抽取瞬态大电流。如果供电路径阻抗过高,这些电流就会在电源平面产生电压降落,形成纹波噪声,进而耦合到信号线,引发时序违例甚至系统崩溃。PCB电源去耦策略的本质,就是在正确位置、以正确方式提供局部低阻抗电流通道,让芯片“就近取电”,避免远距离传输带来的寄生效应。

为什么去耦电容是首选武器?

去耦电容(也称旁路电容)能在高频下呈现低阻抗,为芯片提供瞬时电流储备,同时滤除电源平面上的高频噪声。相比加粗电源走线或增大平面面积,电容方案成本低、效果显著,尤其在多层板设计中无可替代。

一个经典实验可以直观说明其价值:在一块未加去耦电容的FPGA开发板上,让核心以最高频率运行,电源轨纹波可达200mV以上;仅在每个电源引脚对附近添加0.1μF陶瓷电容,纹波立刻降到30mV以内,系统稳定性大幅提升。这不是理论推导,而是无数项目验证过的现实。

去耦电容选型:不止看容值

很多新人第一反应是“多加几个0.1μF就行了”。这种“一刀切”思路在低速电路或许凑合,但在GHz级高速设计中注定失败。正确的PCB电源去耦策略需要综合考虑容值、封装、ESR/ESL和频率响应。

1. 容值组合覆盖全频段

单一只用0.1μF只能有效抑制100MHz~500MHz噪声。更全面的方案是采用多容值并联:

- 0.01μF~0.047μF:针对GHz以上极高频

- 0.1μF:经典值,覆盖大多数数字开关频率

- 1μF~10μF:中低频瞬态响应

- 10μF~100μF(电解或钽):补充 bulk 储能

这种“金字塔式”组合能让PDN(电源分配网络)在宽频带保持低阻抗。

2. 封装决定寄生参数

封装越小,寄生电感(ESL)越低。优先顺序:0201 > 0402 > 0603 > 0805。实际测试显示,同一容值的0.1μF电容,0201封装在1GHz以上的有效去耦半径比0603大30%以上。

3. 材料与耐压

高频首选X7R或X5R陶瓷电容,NP0/C0G虽温度稳定性更好但容量小,主要用于精密模拟电路。耐压至少为额定电源电压的2倍以上,避免击穿风险。

4. 反谐振问题

不同容值并联时可能出现反谐振峰,导致某些频点阻抗反而升高。解决办法是错开容值比例(如0.01μF、0.1μF、1μF、22μF),或借助仿真工具查看PDN阻抗曲线。

布局黄金法则:距离才是王道

再好的电容,摆放位置不对也白搭。去耦电容布局原则的核心只有一句话:让电流环路面积最小。

- 就近原则:电容焊盘到IC电源引脚的走线长度(含via)应控制在2mm以内,最好直接放在IC正下方或同侧。

- Via优化:电源和地分别用独立via连接到内层平面,避免共享via增加电感。via间距越近越好,多个via并联更佳。

- 电容朝向:焊盘应朝向IC,让电源先流经电容再进入芯片(Power → Cap → IC),而不是反过来。

- 平面层设计:电源平面与地平面必须相邻(最好紧挨),形成最小分布电容。禁止电源走宽线代替平面。

- 分组布局:高功率模块(如CPU、FPGA)单独集中大量去耦电容;低噪声模拟区与数字区分开供电,避免串扰。

一个被反复验证的PCB去耦电容最佳实践:在四层板上,将去耦电容全部放在顶层,电源via直接下到第二层电源平面,地via下到第三层地平面,第四层补信号。这种紧凑结构能将环路电感降到nH级。

高级优化:从经验到仿真驱动

经验规则能解决80%问题,但顶级设计必须引入PDN仿真。

1. 目标阻抗法

计算芯片最大瞬态电流I_max和允许纹波V_ripple,得到目标阻抗Z_target = V_ripple / I_max。通常要求在DC~数百MHz范围内,PDN阻抗低于Z_target。仿真软件(如HyperLynx、Sigrity)可直观显示频率-阻抗曲线,指导电容数量和位置调整。

2. 平面腔谐振抑制

大面积电源平面容易在特定频率产生驻波谐振。解决办法:在平面边缘均匀分布小容值去耦电容,或在谐振节点位置添加阻尼电容。

3. 多板协同

在系统级设计中,主板与模块板需协同去耦。模块板负责本地高频去耦,主板提供大容量bulk电容和低频滤波。

常见误区与避坑指南

- 误区一:认为电容越多越好。过度堆叠会导致反谐振和成本浪费。通常每个电源引脚对1~3个电容足够。

- 误区二:只在电源入口放大电解电容。bulk电容只能应对低频,无法抑制高频开关噪声。

- 误区三:忽略焊接工艺。手工焊接时高温可能导致MLCC容量衰减,建议采用回流焊并预留温降裕度。

- 误区四:四层板无法做好去耦。实际通过合理层叠和via阵列,四层板也能实现优秀电源完整性。

真实案例拆解

某款5G通信模块初期测试时,在满负载下出现随机掉线。排查发现3.3V电源纹波达150mV,远超芯片规范。原设计仅在FPGA每组电源引脚放了2个0.1μF电容,且距离达5mm。优化后措施:

- 在每个电源引脚正下方新增0201封装0.01μF电容

- 补充4个10μF低ESL聚合物钽电容集中放置

- 调整via布局,使用双via并联

- 在电源入口增加100μF电解电容+铁氧体磁珠滤波

改进后纹波降至25mV,系统再未出现掉线,顺利通过EMC认证。这个案例再次证明:科学的PCB电源去耦策略往往能以最低成本换来最高可靠性。

结语:把去耦当作设计哲学

优秀的PCB电源去耦策略不是简单堆电容,而是贯穿整个设计的系统工程。从原理图阶段就应标注推荐电容清单,到布局阶段严格执行距离规则,再到仿真验证PDN阻抗,每一步都不可马虎。

当你下一次面对电源噪声问题时,不妨先问自己三个问题:

1. 我的去耦电容是否覆盖了所有关键频段?

2. 电流环路是否真的做到了最小?

3. PDN阻抗是否在全频段低于目标值?

答案为“是”,你的电路就离稳定又近了一步。